# Challenges of Expanding Large Area Arrays for Fine Pitch Vertical Probe Cards

Cameron Harker (Presenter)

Sr. Director of Marketing

Yohannes Desta, PhD

Dir. of NPI Engineering

FormFactor, Probes BU

# Agenda

## Motivation of Work

- Continued strong growth in the wire bond, automotive IC market

- Expanding challenges and trends for wire bond probing

- Development Strategy Overview

- Architectural Strategy

- Product Overview

- Product Validation Results

- Internal Validation Results

- External Validation Data

- Summary and Acknowledgements

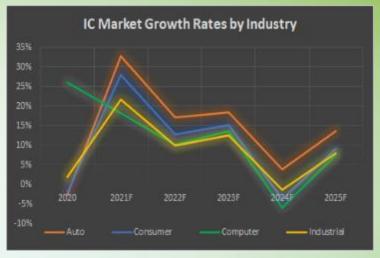

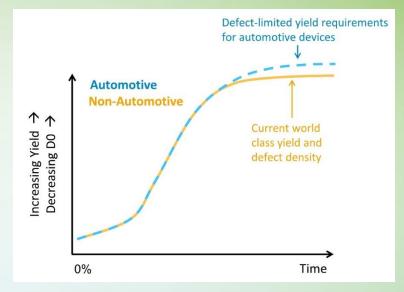

## **Automotive Semiconductor Market Overview**

## Automotive electronics is a fast-growing market

- Automotive IC market forecasted to grow to ~\$40B in 2021

- Forecasted 16.8% CAGR from 2020 to 2025 is the strongest end-use segment (IC Insights 2021 report, June update)

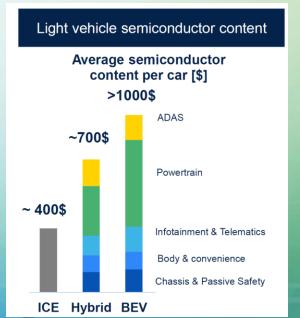

- Value of semiconductors in cars continues to increase with advances in hybrid and electric vehicles

#### Requirements for automotive applications:

- "Unlike semiconductors intended for use in consumer electronics, automotive semiconductors must retain functionality in more extreme environments (colder and hotter temperatures) for longer periods of time"

- The Automotive Semiconductor Market, USITC, May 2019

(IC Insights 2021 report, June update)

## The Impact of Automotive Requirements for Semi Wafer Test

- Critical requirements for automotive semiconductor test

- Test temperature extremes continue to increase

- Structures are typically peripheral pads for wire bond applications

- Pad pitch continues to shrink

- Pad sizes are being reduced to support die size shrinks

- Dense device circuitry under the pads

- Devices can be sensitive to CRES and CRES variation

- Automotive suppliers driving reduced costs

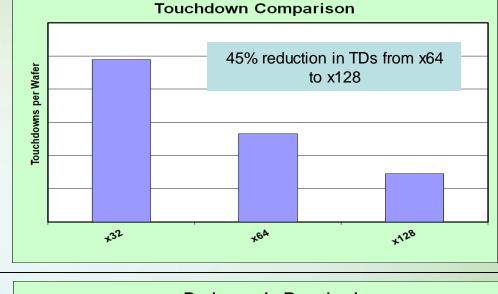

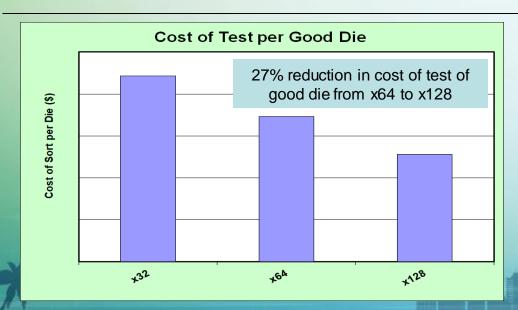

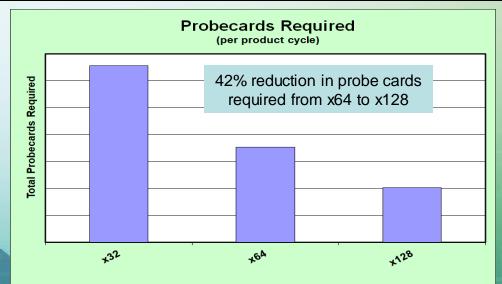

# Meeting Cost of Test Reduction Challenges

- Reduce cost of test with increased parallelism

- TCOO analysis

- Key Assumptions

- 5.0mm x 5.0mm die size

- 300mm wafer

- 30 sec test time

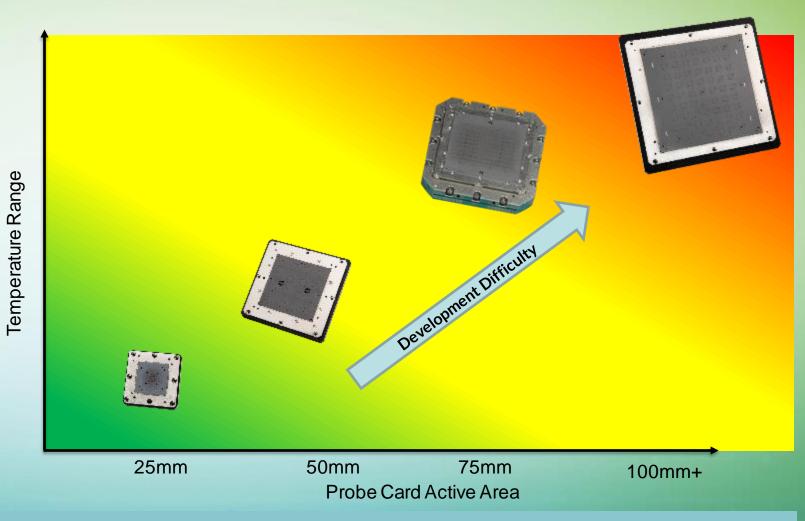

# Increasing Probe Card Active Area

- Increasing parallelism requires increased probe head active area

- Presents significant development challenges to overcome to meet probing requirements

- Must consider critical requirements

- Thermal effects

- Device Layouts

- Pad size/pitch

- Electrical

As PH sizes and thermal requirements increase, CTE mis-match issues become significant challenge to overcome

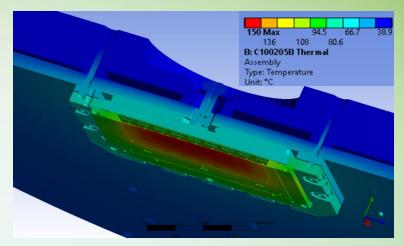

## Large Active Area Vertical PC Material Selection Strategy

- Three step process used to optimize the materials of various LAA probe card components:

- 1. Prediction of thermal gradient on various components of the probe card by use of FEA simulation for the full temperature range

- → Chuck temperature of 150°C, 100°C temperature delta between the coldest and hottest components

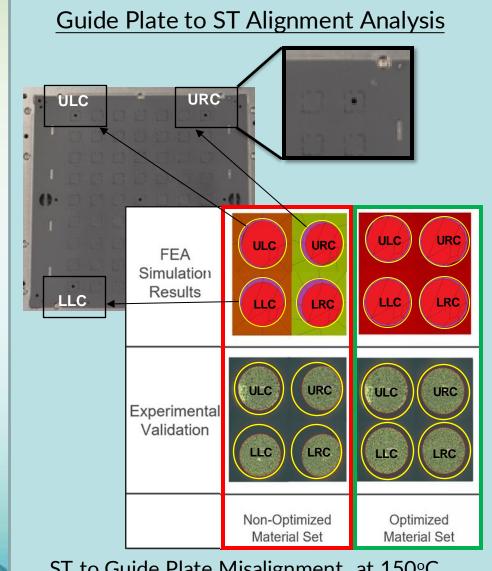

#### 2. Optimal material selection:

- Use thermal gradient derived from step one as input to thermal-mechanical model

- Predict misalignment between various components and select best material combinations

- 3. Experimental validation of optimal material set for the full probe card build

Thermal model of a probe card with prober chuck temperature set at 150°C

#### Model includes:

- 1. Thermal conduction of all parts of the a ssembly

- **2. Contact conductance** between the different horizontal members

- 3. Radiation between the wafer and probe card

- 4. Air conduction between the wafer and P CBA

## Vertical PC Components Material Selection Challenges

| Component                    | Consideration                                           | Solution                     |

|------------------------------|---------------------------------------------------------|------------------------------|

| Guide Plates                 | CTE has direct impact on wafer bond pad size capability | Best match to customer wafer |

| Space<br>Transformer<br>(ST) | ST to probe misalignment                                | Best match to guide plate    |

| Mounting<br>Hardware         | ST to probe misalignment                                | Best match to ST             |

- Based on requirements of peripheral pad probing, FFI developed a solution based on an Multi-Layer Ceramic (MLC) ST

- Advantages include:

- 1. Low to moderate levels of CTE of the MLC → stable thermal-mechanical performance

- 2. ST flatness  $\rightarrow$  good probe planarity

- Optimized material set → stable thermal-mechanical performance

ST to Guide Plate Misalignment at 150°C

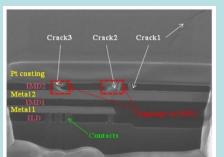

# **Bond Pad Integrity - Minimize Pad Damage**

- "Reliability expectations for automotive devices are <u>orders of magnitude</u> higher than consumer devices"

- Bond pad damage must be held to a minimum both surface area and depth

- Need clean area for bonding the device

- Zero tolerance for ILD cracking for UPC damage

Automotive IC Industry Trends – Semiconductor Engineering – Jan. 2018

|                 | Low Force MEMS<br>Springs                                      | Medium/High Force<br>Springs                                               |

|-----------------|----------------------------------------------------------------|----------------------------------------------------------------------------|

| Spring<br>Force | 1.2 – 1.5 grams at production OT to support minimal pad damage | 4 - 12 grams at production OT - High force can create excessive pad damage |

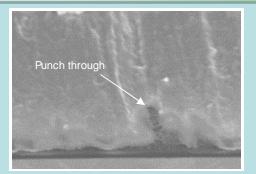

SEM images of pad damage issues causing device failures/issues

## Meeting the Challenges of LAA Vertical Probing

#### Requirements:

- Thermally stable vertical spring architecture to support wide temperature range of automotive test requirement

- Tight pad pitch, multiple pad rows, core pads

- Probe on small pads with minimal pad damage

- Stable electrical performance low, stable CRES

- Increase parallelism to reduce cost of test

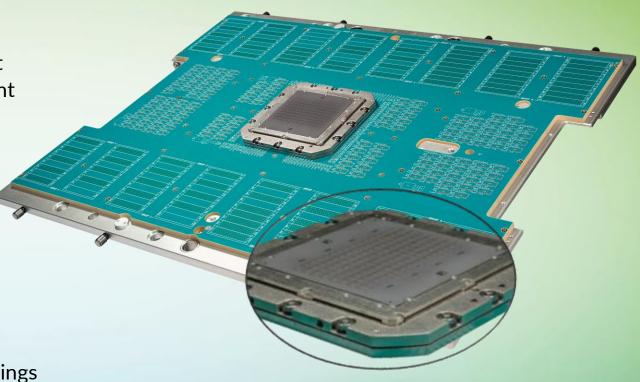

#### Kepler™ Vertical Probe Card Features:

- Utilizes Multi-Layer Ceramic (MLC) space transformer

- Proprietary fine pitch, low force vertical 2D MEMS springs

- Full planarity/tilt adjustment capability

- Flexible probe head configuration to support various device layouts, array sizes and pad pitch requirements

- Service friendly architecture field replaceable springs and components

128 site, 60um Pitch, 10K Probes, V93K DD

# **Experimental and Qualification Results**

- Low force spring performance

- 60um pad pitch capable

- Scrub mark results

- Minimal pad damage and placement

- Thermal performance

- Scrub mark position at temperature extremes

- Planarity results

- Capability at 75mm active area

- CRES performance

- Stability at temperature

- Lifetime study

- Confirm low wear rate

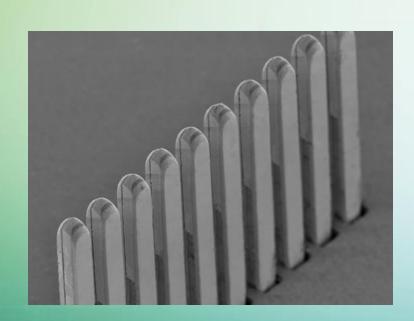

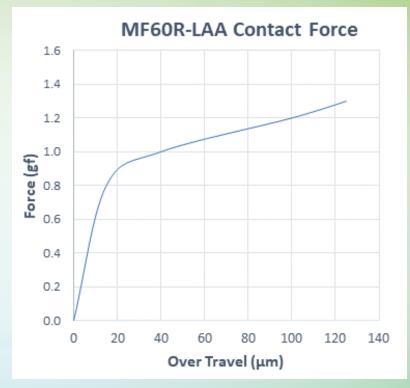

# FFI MF Family Low Force 2D MEMS Spring

Utilizing FFI low force 2D MEMS MF spring family, developed a solution for 60um pitch pads applications

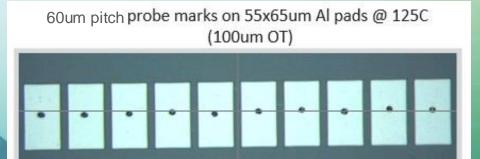

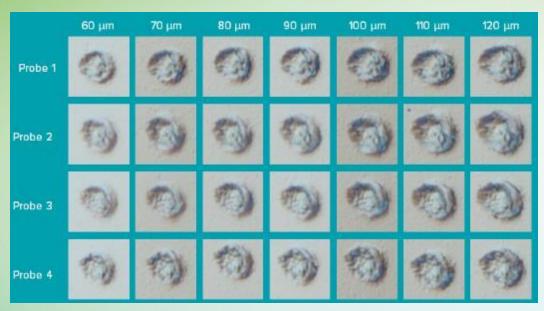

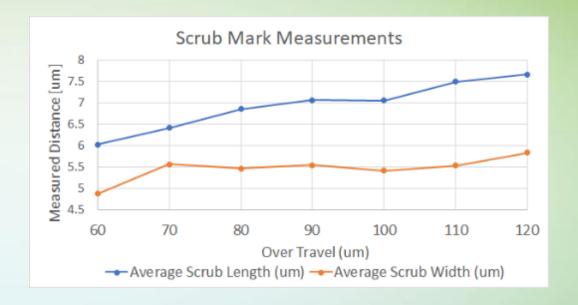

## Scrub Mark Results

Optical images of scrub marks

## MF60R minimizes pad damage

- Small scrub mark from low force vertical spring minimizes pad damage area

- Very low risk of punch through due to small scrub mark with minimal lateral scrub

# Kepler™ Thermal-Mechanical Performance

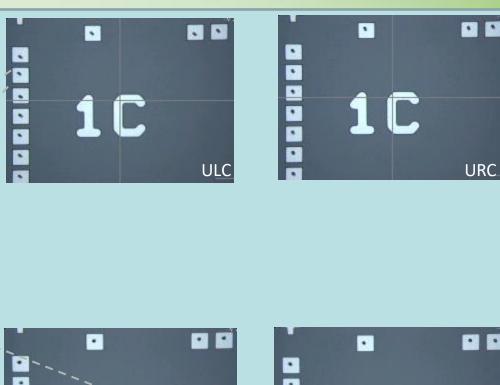

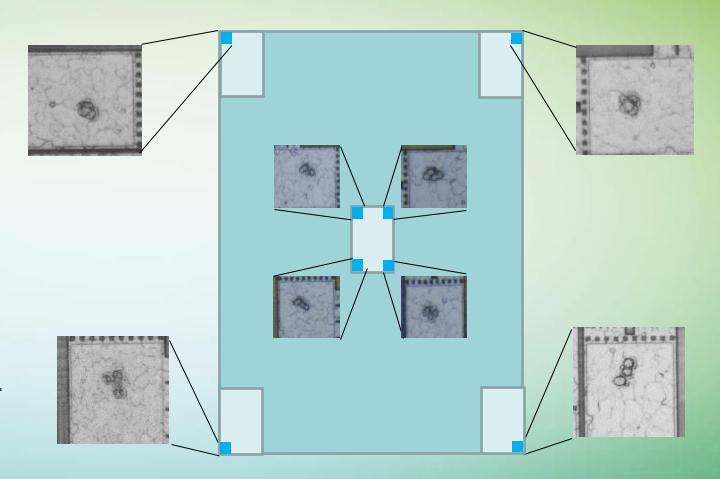

#### Experimental Set-up:

- Parallelism: x128

- Array size: 42mm x 72mm

- Pad size: 55um x 55um

- TD data collected at -40°C, 25°C and 150°C

- Scrub mark images from upper right corner of die from four corners of the array

Scrub marks from temp range of 190°C landing in same pad area across the full PH array

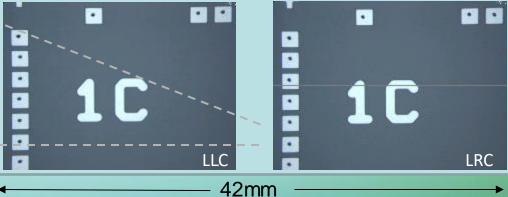

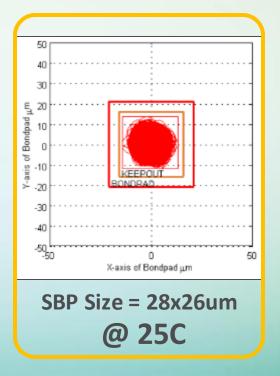

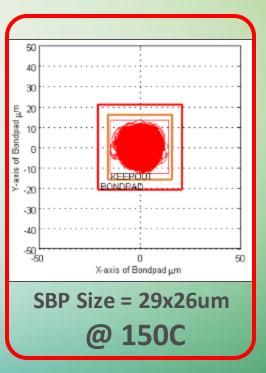

## Super Bond Pad Capability at Full Temp Range

### Super Bond Pad (SBP):

- Consolidation of scrub marks superimposed on top of each other to establish a single virtual pad representing all scrub marks

- SBP calculation removes systematic errors not associated with the probe card capability

- Parallelism: x128

- Array size: 42mm x 72mm

Pad size: 42um x 42um

Keep out: 5um

100% of scrubs in pad area

meeting the keep out spec

SBP performance <30um per side through entire temperature range

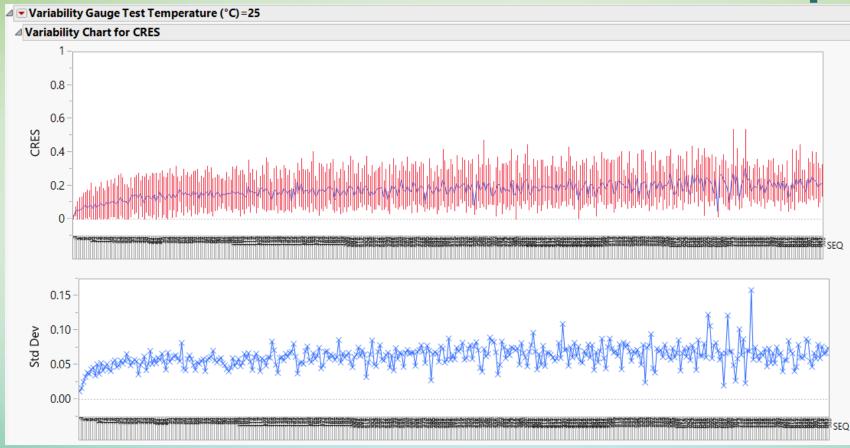

# **CRES Performance at Room Temperature**

Test Conditions: 1000 TD on blank Al wafer at 100um OT

**Kepler**<sup>™</sup> achieves low and stable CRES

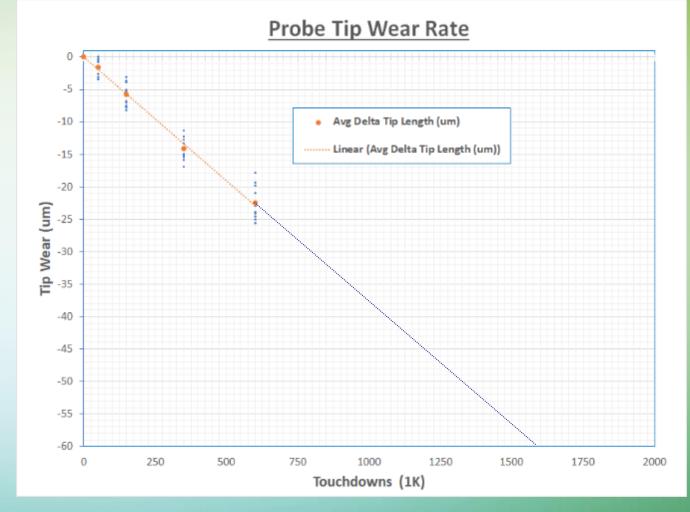

# Wear Rate Study Results

### **Objective:**

Establish probe tip wear rate during production use case

#### **Experiment:**

- Accelerated study 100um OT on Al pads

- Tip length was measured at 50K, 150K, 350K and 600K TDs

- Continue to measure tip length at every 500K TD intervals

- Optimized cleaning recipe with WA6000-SWE

Data projects >1.5M TD lifetime

# Large Active Area Planarity Performance

Planarity measured on PRVX on large active area array:

Array size: 42mm x 72mm

Parallelism: x128

Measured outgoing planarity <20um on entire array</li>

| Planarity | Min.   | Max.   |

|-----------|--------|--------|

| 19.9 um   | -7.9um | 12.0um |

PH Planarity (um)

- 10.0

- 7.5

- 5.0

- 2.5

- 0.0

- -2.5

- -5.0

- 7.5

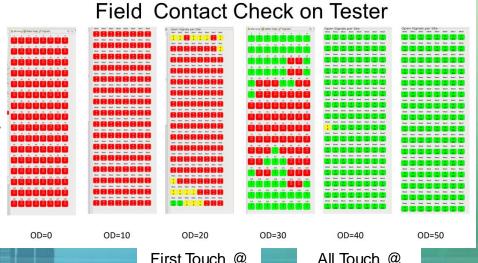

Incoming planarity collected with contact check for first to last electrical touch confirmed ~25

planarity across full array

First Touch @ 20um OD

All Touch @ 40um OD

## Thermal-Mechanical Performance - Customer Validation

### Experimental Set-up:

- Parallelism: x128

Array size: 42mm x 72mm

- Pad size: **42um** x **42um**

TD data collected at 150°C,-40°C,

25°C and repeated at 150°C

Scrub marks at all edges of the array landing in very small area – minimal pad impact

Architecture demonstrating very stable scrub mark placement from -40°C to 150°C

## Summary

- Strong automotive IC market growth requiring large active area solutions for wire bond applications

- FFI has developed a large active area vertical probe card solution

- Addressed challenges related to CTE mis-match to meet increasing test requirements

- Thermal-mechanical stability over wide temperature

- Tight pad pitch

- Small pad sizes

- Tight planarity and scrub mark position

- Stable and low CRES

- Long life-time

- Flexible low force vertical MEMS architecture to reduce cost of test with increasing multi-site capability

# Acknowledgements

## Special thanks to:

- Mark Ojeda Infineon Technologies

- Pouya Dastmalchi FormFactor

- William Deas FormFactor

- Doug Ondricek FormFactor