### Fully Automated Integrated Silicon Photonic Wafer Test

Golam Bappi (Ayar Labs) Dan Rishavy (FormFactor)

### Overview

- Introduction to Ayar Labs

- Early Characterization Setup

- FormFactor CM300-Silicon Photonics Probe Station

- Overview of Test Executor

- Improving Test Throughput

- Improved Test Flow

- Current Work: Low Loss Wafer Level Edge Coupling

- Future Work: Probe Card for Wafer Level Electrical-Optical Probing for KGD

## Introduction

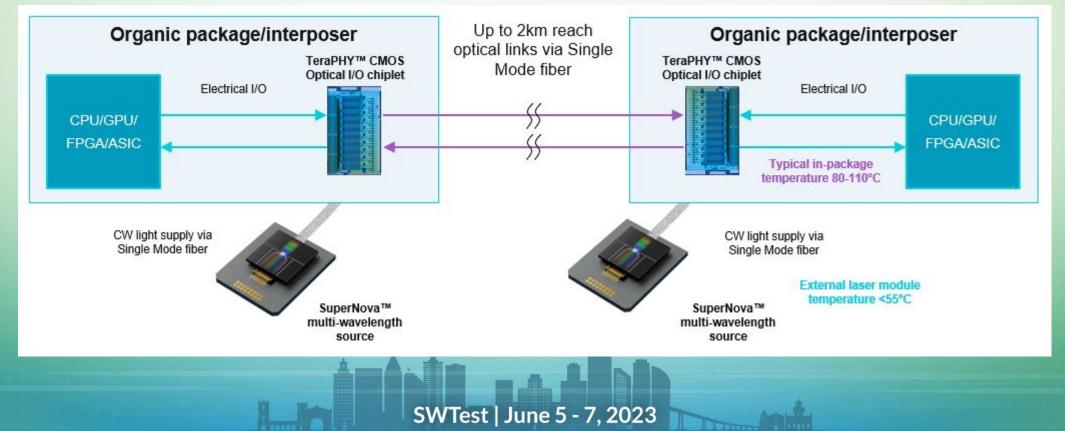

- Ayar Labs develops monolithic optical I/O chiplets (TeraPHY<sup>™</sup>) to enable high bandwidth, low latency, and low power consumption interconnects for chip-to-chip communication

- Applications

- High performance computing

- Disaggregated memory/compute architectures

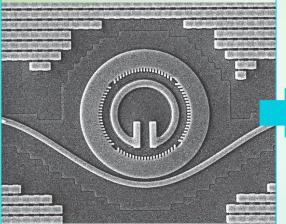

### **Micro-ring Resonators**

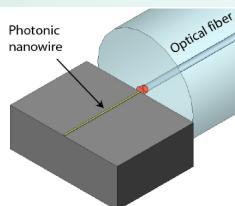

- Up to 1,000x smaller than optical devices in traditional ethernet transceivers

- High-speed capability

- Compatible with high volume 300mm CMOS<sup>1</sup>

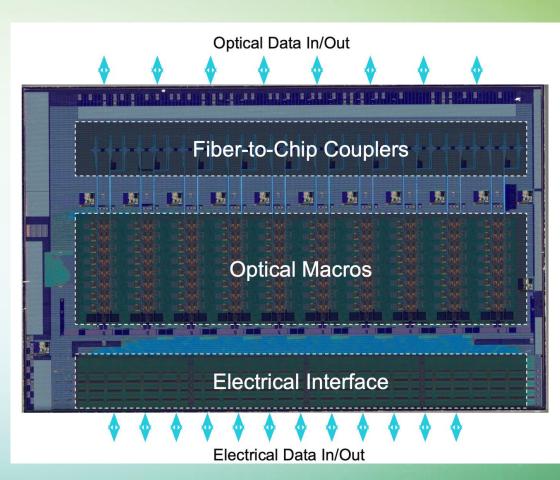

**Monolithic Integration**

Dense integration of all electronics (TIAs, drivers, equalization, control) and photonics (waveguides, modulators, detectors) on a single CMOS chip

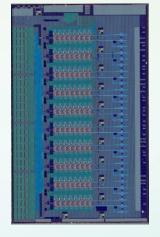

Optical I/O chiplets

- TeraPHY<sup>™</sup> chiplet for in-package optical I/O

- Multi-Tbps with <5pJ/bit

- Nanosecond latency (no FEC required)

### SoC In-Package Integration

- Integration with

state-of-the-art FPGA

- Direct from the package optical I/O

nounces-next-generation-silicon-photonics-solutions-and/

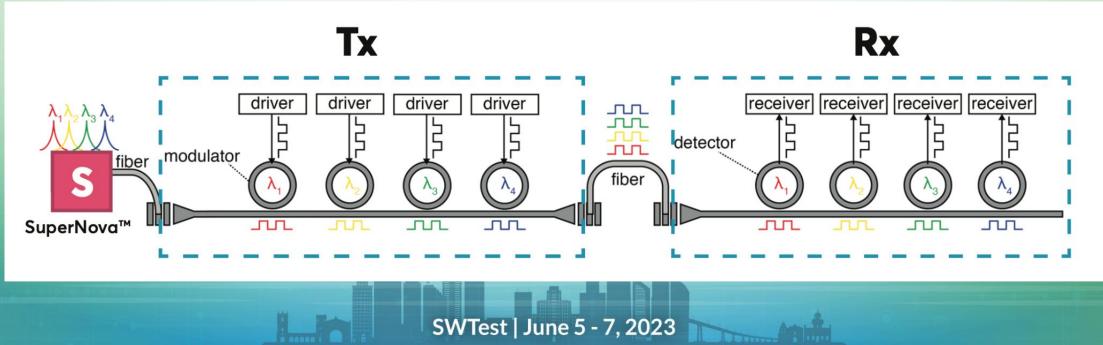

- Multi wavelength laser source for encoding data on multiple streams simultaneously

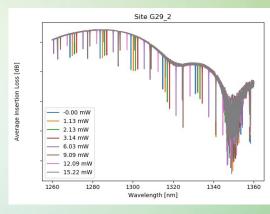

- Tunable microring modulators modulate transmission of specific laser wavelengths based on electrical data pattern input

- Microring resonators on receiver demuxes incoming data on specific wavelengths for conversion to electrical data pattern output

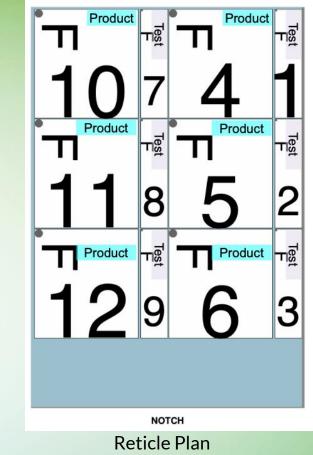

- Reticle contains product and test chips

- Product chip

- Horizontal edge couplers for optical connectivity

- 1400 bumps for electrical connectivity

- How do we screen for known good die?

- Electrical wafer sort on standard 93k ATE

Traditional VLSI probe card -> no optical connectivity

Horizontal edge coupler SWTest | June 5 - 7, 2023

- Optical link is composed of multiple electronic + photonic components

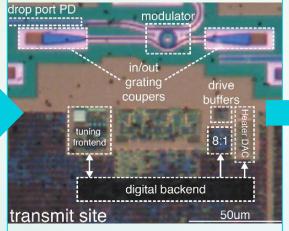

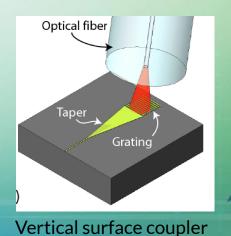

- During NPI, we had test chips alongside product chips which contain independent device sites using vertical surface couplers

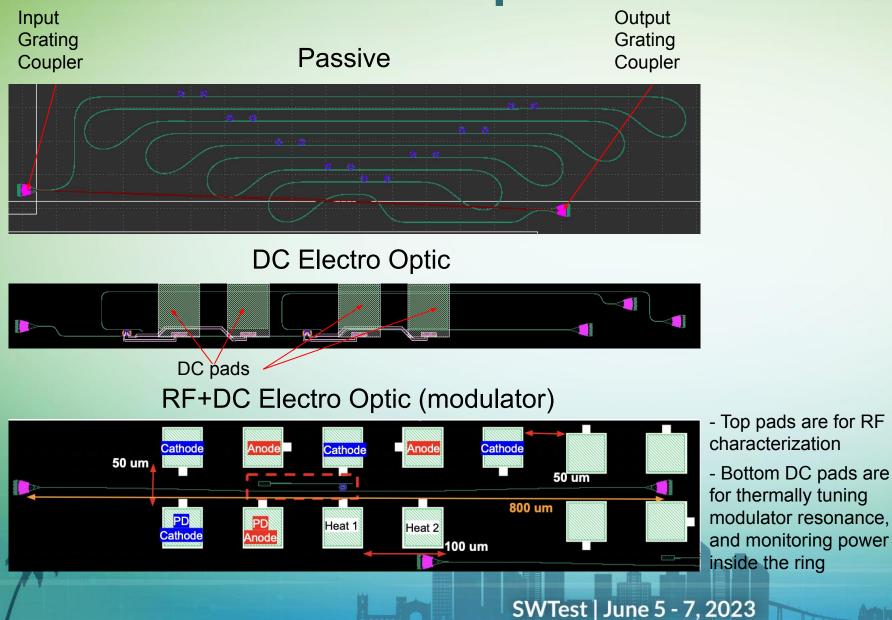

- Microring resonators (MRR)

- Tx modulators (doped junction for electro-optic response)

- Rx ring filters to select particular wavelength

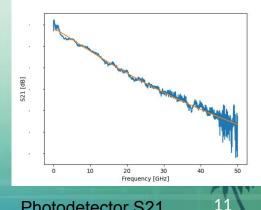

- Germanium photodetectors

- Waveguides, NxN optical couplers, polarization splitter/rotators

- Thermal phase shifters

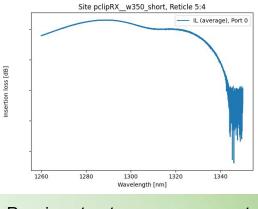

- Detailed high volume characterization of the components above is used to build a link model and estimate yield of product

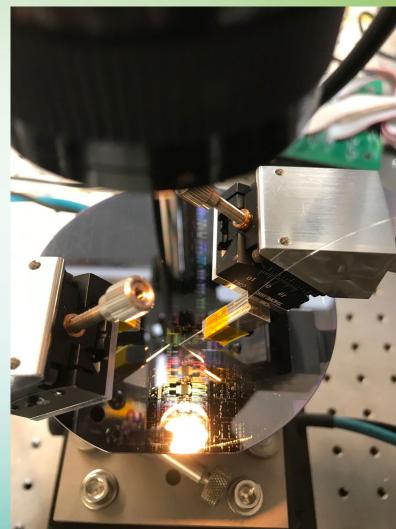

## **Early Characterization Setup**

- Manual test station

- Issues with repeatability and stability of two fiber setup (~0.5 dB)

- Low throughput due to time it takes to align fibers after stepping them from site to site

- Difficult to accurately set fiber height

- No testing over temperature

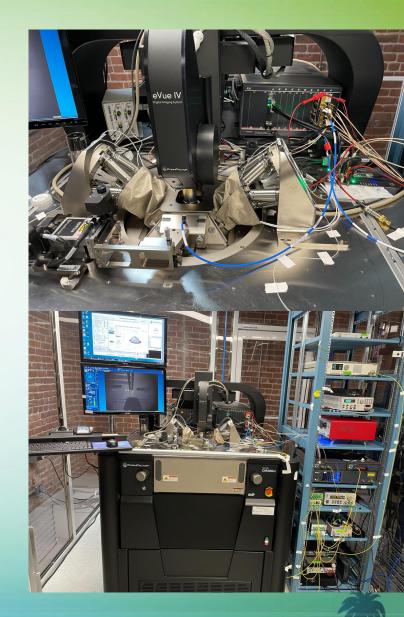

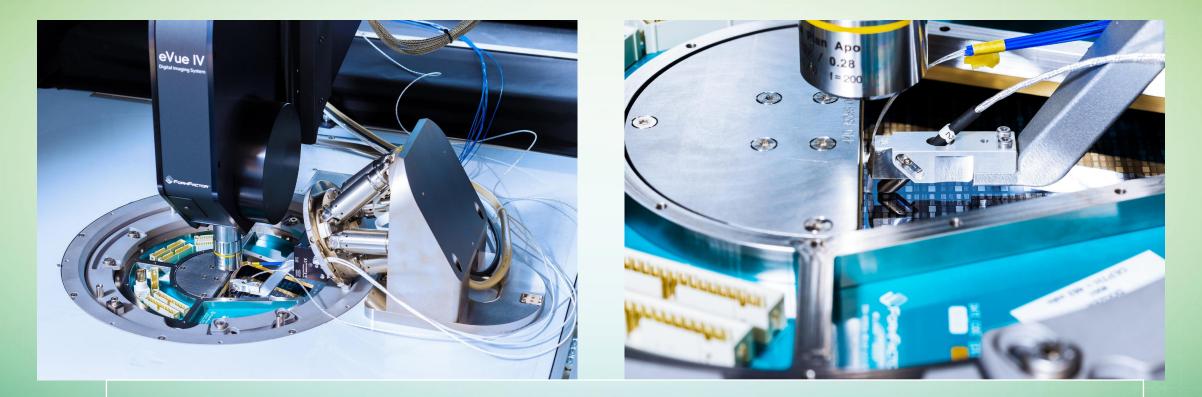

### **CM300xi - SiPh Probe Station**

<u>SWTest | June 5 - 7, 2023</u>

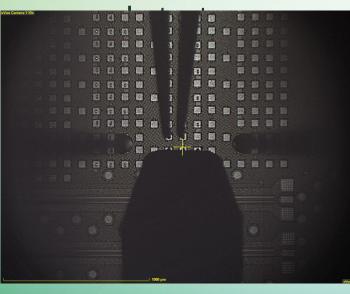

- Enables automated full wafer optical + electrical characterization of various components that are used to build the TeraPHY<sup>™</sup> chiplet

- Repeatable fiber alignment (~0.1 dB)

- Enables testing at high temperature (up to 150°C)

### **CM300xi - SiPh Probe Station**

- Enables automated full wafer optical + electrical characterization of various components that are used to build the TeraPHY<sup>™</sup> chiplet

- Keysight swept laser system (Mueller matrix)

- Optical switches

- Polarization stabilizer

- Variable optical attenuator

- O-band amplifier Optical backscatter reflectometer

- PCB to enable fiber alignment using photodetector current from DUT on wafer

- Source measure units

- Keysight PXI network analyzer (up to 53 GHz)

- Thorlabs reference transmitter (up to 65 GHz)

- Bit error rate tester and pattern generator remote head (up to 32 GBaud)

- Keysight sampling oscilloscope

probe station

0

### **Examples of Test Sites**

#### Passive structure measurement

#### Thermal phase shifter

Photodetector S21

### CM300xi-SiPh Test Executor

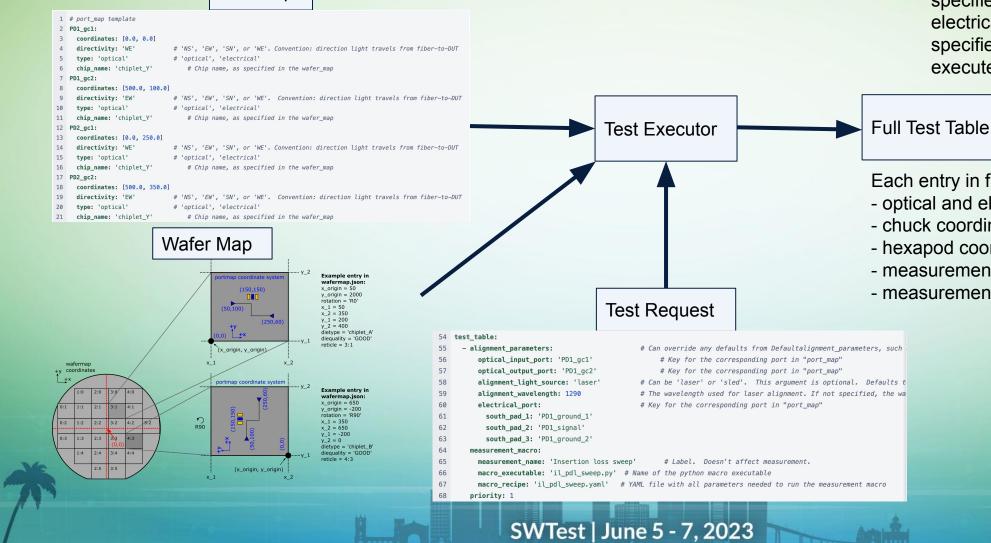

#### Port Map

Wafer Map: Coordinates and dimensions of every subdie on wafer Port Map: Coordinates of every optical port (grating coupler) and electrical port relative to subdie origin Test Request: A table where each entry specifies a set of optical and/or electrical ports for a test site. It also specifies the measurement routine to execute and its parameters.

Each entry in full test table contains:

- optical and electrical ports in test site

- chuck coordinates

- hexapod coordinates

- measurement macro to execute

- measurement parameters

## **Improved Test Flow**

- Test throughput is still limited due to multiple factors

- Electrical probes need to be manually lowered/lifted. It is not possible to run electrical only or electro-optic tests, along with passive measurements.

- Time taken to reconfigure and calibrate setup when switching between various types of measurements can be significant (1h ~ half day)

- Ex. Two tier VNA calibration for RF measurements such as S11 (capacitance) or bandwidth (S21)

- Test workflow

- Set up hardware for passive test

- Test wafer 1, wafer 2, ...

- Set up hardware for DC electrical only, and DC electro-optic test

- Test wafer 1, wafer 2, ...

- Set up hardware for RF electrical only and RF electro-optic test

- Test wafer 1, wafer 2, ...

### **Improved Test Flow**

- Motorized positioners for allow us to achieve greater test integration

- Both RF and DC probes are loaded from south and north side respectively

- Probe is lifted and retracted when not needed for a given measurement

- RF calibration is monitored for drift, and periodically re-calibrated on ISS

Optical fibers, DC probe, and RF probe at home site

- Optical fibers and DC probe used for measurement

- RF probe lifted and retracted since it is unused

SWTest | June 5 - 7, 2023

Optical fibers used for measurement

DC and RF probe lifted and retracted since they are unused

## Summary

- CM300xi-SiPh probe station enables us to characterize various electronic/photonic structures at scales needed to obtain statistical distributions with high confidence

- These parameters allow us to predict system performance

- Motorized positioners allow for significantly increased test throughput

- Any combination of passive, DC, DC electro-optic, RF, and RF electro-optic measurements can be run over full wafer with no test setup re-configuration and calibration

### **Current Activities and Future Work**

## **Ongoing Test Challenges**

- We want to have greater optical and electro-optical functional characterization of the actual TeraPHY<sup>™</sup> product chiplet at the wafer level

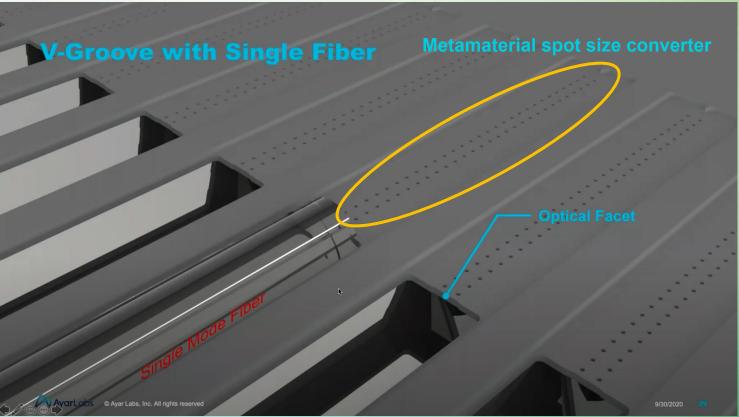

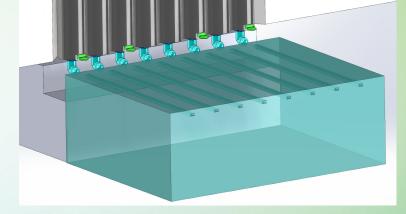

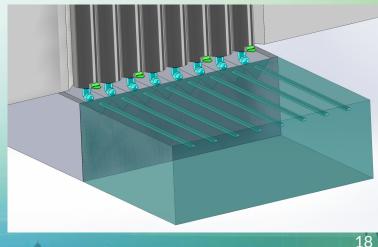

- Requires probing at the wafer level through V-grooves for optical connectivity

- Simultaneously need probe card that can land on all bump locations for electrical connectivity

### Current Work - Low Loss Wafer Level Edge Coupling

V-Groove

Or Trench

Wafer Level Trench

Wafer Level V-Groove

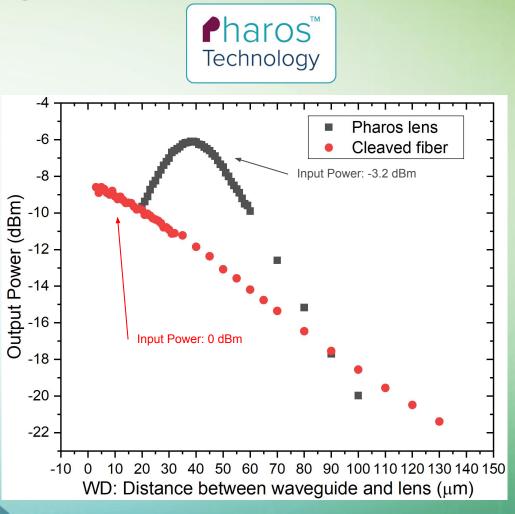

### **Pharos Low Loss Lens Performance for Edge** Coupling

Singulated Chip: FF Pharos Lens: Structure: Best coupling:

Chip1 MFD = 9 um MFD = 6.0umLoopbacks Edge Facet WD=5um (Cleave fiber array) Power =-8.5 dBm Coupling loss is 4.25 dB/facet WD=38um (Pharos Lens) Power= 6.01-3.2 dBm Coupling loss is 1.47dB/facet

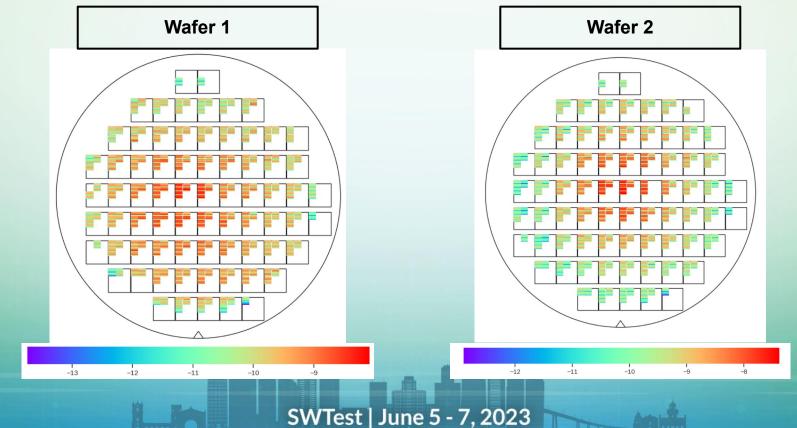

## **Application of FFI Pharos Technology**

- Ayar Labs has performed full wafer measurements on dozens of wafers

- Insertion loss metric is being used as KGD screening criteria

### Future Work – FFI Apollo Probe Card with Wafer Level Edge Coupling

Fully Automated Wafer Level Co-Packaged Optics Electrical-Optical Probing

### Acknowledgements

- Forrest Sedgwick (Sr. Director of Test Engineering at Ayar Labs)

- Derek Kita (Sr. Staff Optical Design Engineer at Ayar Labs)

- Michael Rust (Sr. Staff Photonic Test Engineer at Ayar Labs)

- Neil Sapra (Sr. Photonic Design Engineer at Ayar Labs)

- Quan Yuan (Optical Design Engineer at FormFactor)

- Joe Frankel (Systems Engineer at FormFactor)

- Mike Simmons (Mechanical Design Engineer at FormFactor)