True Kelvin CMOS Test Structure to achieve Accurate and Repeatable DC Wafer-Level Measurements for Device Modelling Applications Dr Sia Choon Beng Choonbeng.sia@cmicro.com ICMTS 2017, Grenoble France

- Challenges for Wafer-Level DC Modeling Measurements

- Typical Probe Contact Resistance vs Scrub Length

- Proposed Test Structure Design

- Experimental Setup

- Characterizing Probe R<sub>C</sub> on Test Pads

- Results & Discussions for NMOS measurements

- Recommendations

- Conclusions

#### Challenges for Wafer-Level DC modeling measurements

- Achieve <u>Accurate</u> & <u>Repeatable</u> measurements at Different Temperatures

- Reduction in Device Channel Resistance Rds

- Probe parasitic resistances are Not Negligible!

- Reduction in Pad size (30x30µm to 20x20µm)

- Smaller tips = large contact resistance

- Continue using low cost Cantilever probecards requiring longer probe scrub

- How to ensure low Probe R<sub>c</sub> at different test temperature?

- Probe on fresh metallization for 3 times or more on pads  $\leq 30x30 \mu m$

- Cu Backend Interconnects underneath AI capped pads

- When exposed, underlying Cu oxidizes rapidly at high temperature

- Test Wafers goes through thermal cycles, how to repeat the test results 1 year later?

- Wider Thermal test range

- From -40 to 125 Deg C to -50 to 175 Deg C

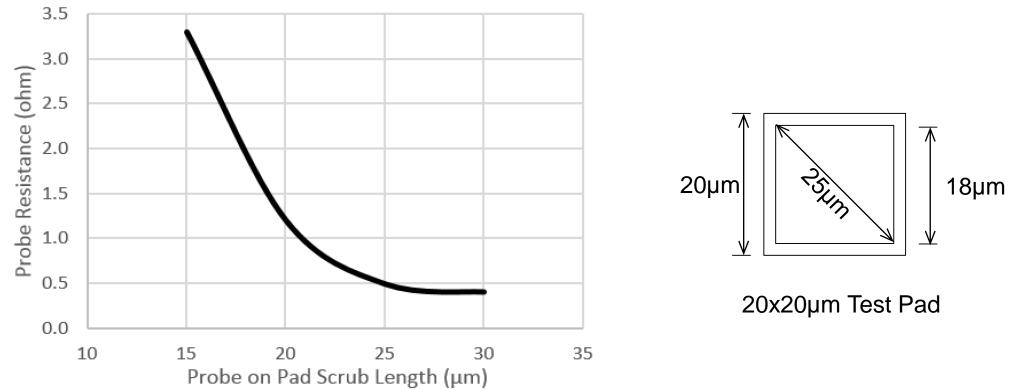

# Typical Cantilever Probe R<sub>c</sub> vs Scrub Length

- > 25 $\mu$ m scrub needed for low probe R<sub>C</sub>

- Challenging to support 20x20µm pads (Diagonally only 25µm)

- How to get sufficient scrub, 3 times on the same pad?

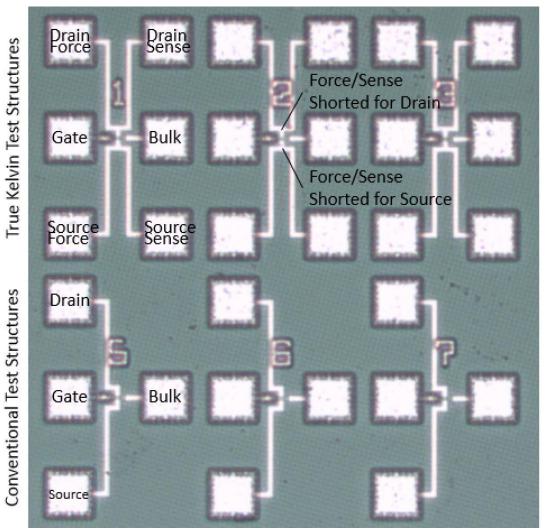

# Proposed Test Structure Design

- 60nm CMOS devices

- Conventional Test Structure

- 4 test pads

- Parasitic Resistances not corrected.

- Probe Kelvin Test Structure

- 6 test pads

- Source/Drain with additional Sense (Test Leads and Pads)

- Parasitic Resistances are corrected.

- Post layout parasitics simulations

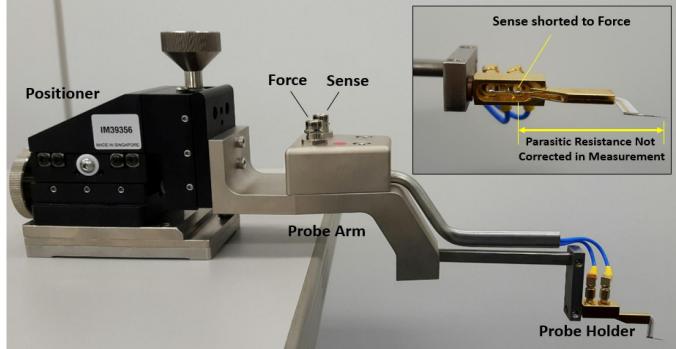

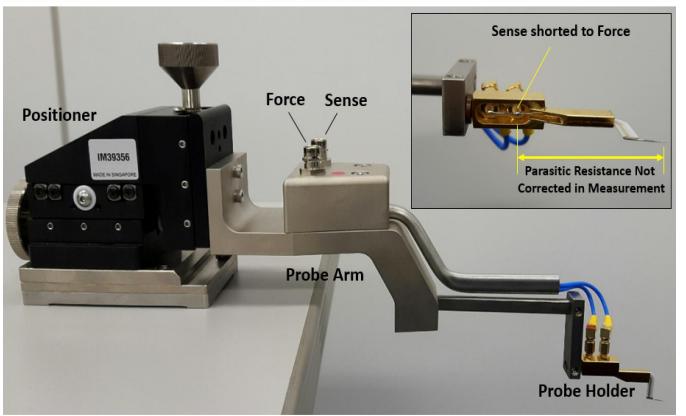

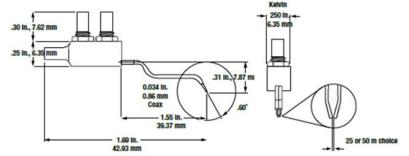

### Experimental Setup

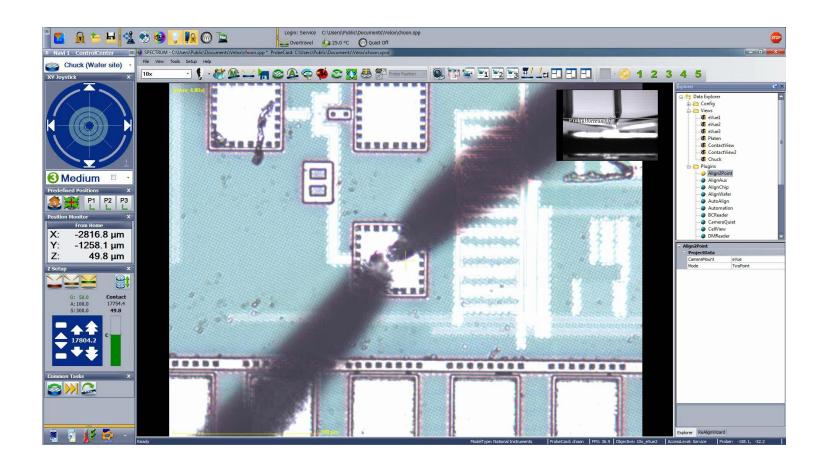

- Test Wafer with 60nm CMOS devices

- Cascade Shielded Probe Station

- Keysight Semiconductor Parametric Analyzer B1500

- Single Probe positioner used instead of probecard for test flexibilities

- 2 probes on same pad

- 30µm probe scrub

- Ensure low Rc

- 100 contact cycles

- Re-probing on the same spot

- Worst-case testing

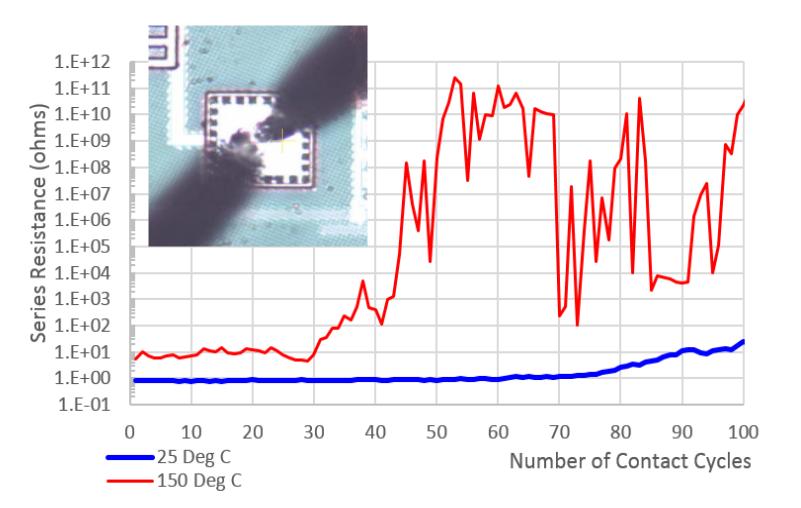

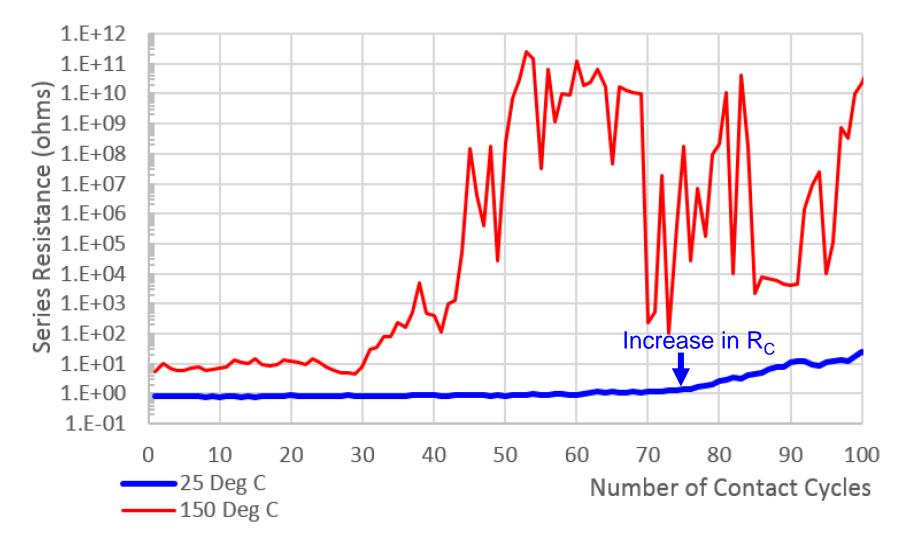

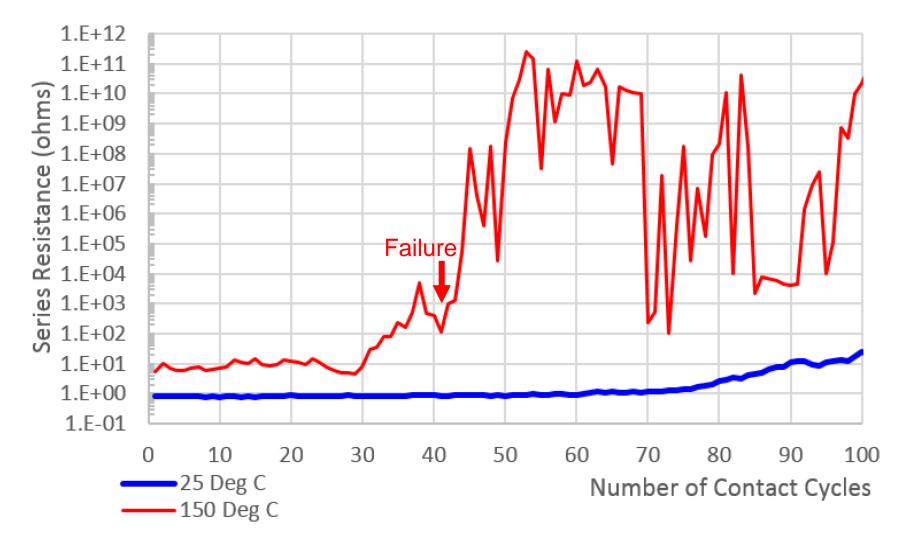

- 25 Deg C Test

- 1<sup>st</sup> 75 Contact Cycles

- 0.8 to 1 ohms

- 100<sup>th</sup> contact cycles

- 20 ohms

- 150 Deg C Test

- Replaced Tips & Check

Probe R<sub>c</sub> at 25°C

- 1<sup>st</sup> 30 Contact Cycles

- about 5 ohms

- 43<sup>rd</sup> contact cycle, underneath Cu oxidizes, resulting in open circuit

# Characterizing Probe RC on Test Pads

Each Probe Parasitic Resistance

- @ 25 Deg C = 0.4 ohms

- @ 150 Deg C = 2.5 ohms

- Too large for advanced devices with decreasing Rds.

- Probecard will also have such large parasitic resistance if sense lines are not close enough to the device terminals.

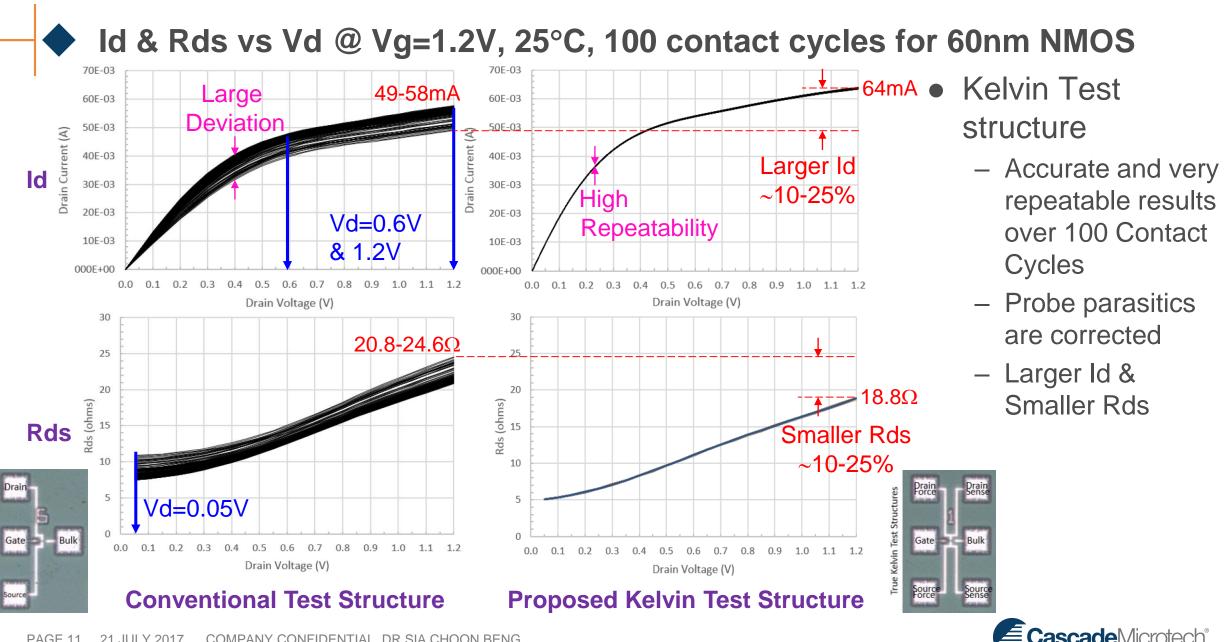

# Results & Discussions for NMOS Measurements

a FormFactor company

PAGE 11 21 JULY 2017, COMPANY CONFIDENTIAL, DR SIA CHOON BENG Email: choonbeng.sia@cmicro.com

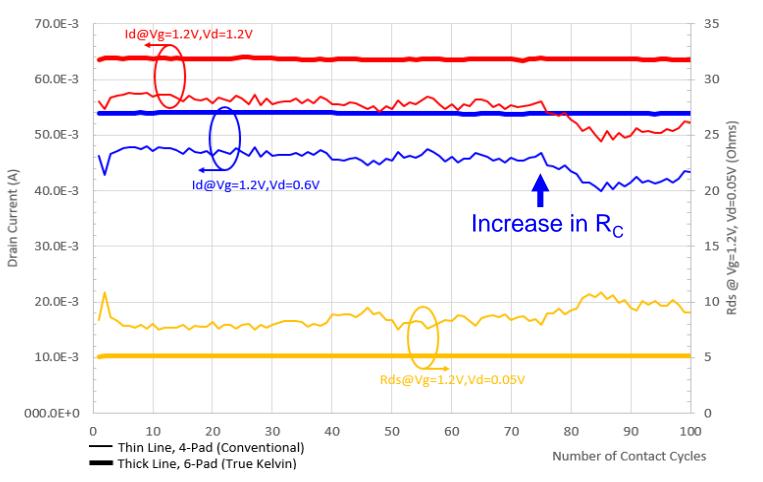

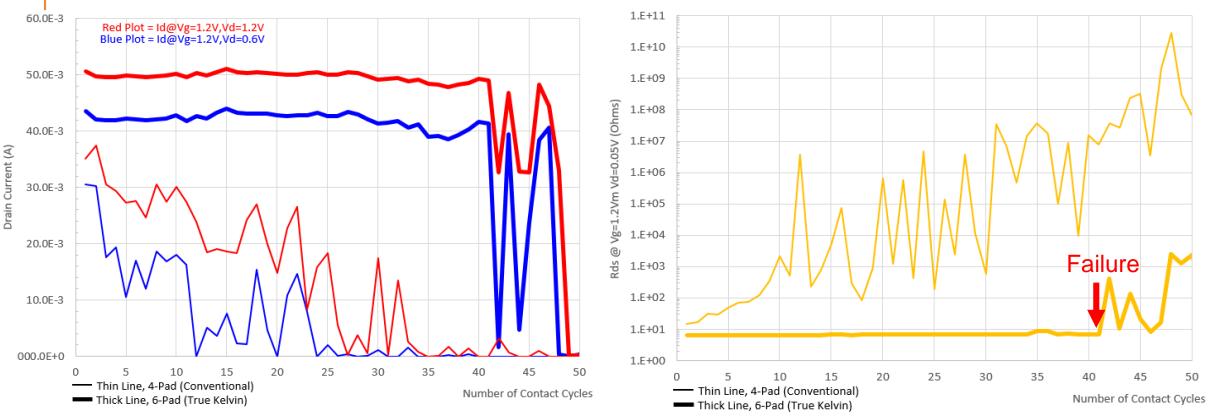

#### Id & Rds vs 100 Contact Cycles @ 25°C for 60nm NMOS

- Kelvin vs Conventional Test Structure

- Measured Id & Rds is extremely <u>stable &</u> <u>repeatable</u> throughout 100 contact cycles.

- Sense line of B1500 is able to correct and mitigate the increase in Rc.

- Probe tip cleaning not required.

#### Id & Rds vs 50 Contact Cycles @ 150°C for 60nm NMOS

- Kelvin Structure

- 1<sup>st</sup> Contact Cycle, Id larger by 30%, Rds much smaller

- 43<sup>rd</sup> Contact Cycle, failure due to underlying Pad Cu fully oxidized

# Recommendations

- Recommended Test Sequence:

- Hot Temp  $\Rightarrow$  Room Temp  $\Rightarrow$  Cold Test

- Test Structures are not probed yet, minimize exposed Cu oxidation

- Adopt an Inert Test Environment

- Adopt Thicker Al. top cap layer

- Adopt Larger Pad (Fresh Metallization)

- Invest in Vertical Probe Card with frequent Tip Cleaning Cycles

- Possible to minimize probe parasitics

- Test Leads not corrected, affects Model accuracy

- Invest in True Kelvin Probe Tips

- Bigger or Longer pads to accommodate 2 Tips

- Test Leads not corrected, affects Model accuracy

- Adopt True Kelvin Test structure

# Conclusions – Adopt True Kelvin Test Structure as it...

- Corrects Probe parasitic resistances (Vary with Temperature).

- Corrects Test Leads parasitic resistances

- Models should not account for test leads).

- Minimizes Retest & Revalidation

- Allows repeated probing of Same Device without Accuracy Degradation.

- Example: Retesting of Golden Wafer for Model development after 1 year of model release

- Allows handling of small test pads < 30x30µm with cantilever probecard

- Using smaller probe scrub and smaller probe tips

- No Probe Tip Cleaning required!

- if B1500 has sufficient voltage headroom to correct for Parasitic Resistances.

- Mitigates  $\uparrow R_c$  due to oxidation of underlying Cu underneath test pads.

- Though larger layout, provides Accurate Results with Lower Cost of Test

# Thank You!Questions?