### MEMS Probe Technology for Fine-pitch CuPillar Bump Wafer Sort Test

# Agenda

### Introduction

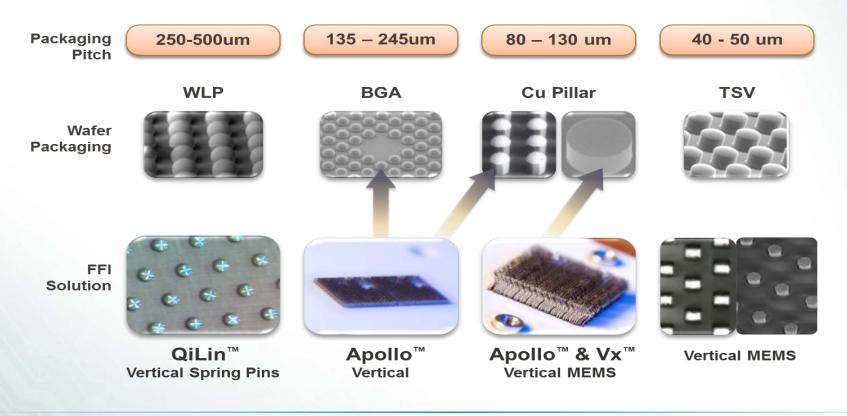

#### Market overview

- SoC chip packaging trend & driving force of CuPillar packaging

- Test challenges on fine pitch CuPillar HVM probing

#### FormFactor Apollo MEMS MF Probe Product Introduction

- MEMS Probe Alignment Control

- Vertical and Lateral Probe Force Impact Probe Mark

- 2x Current Protection on MEMS Probe

- MEMS Probe Life-time Projection

- Automated machine probe insertion

- Case studies:

- probe card uptime, probe lifetime data, yield comparison

#### Conclusion

- Formfactor Product portfolio and 2017 Market Share

- conclusion

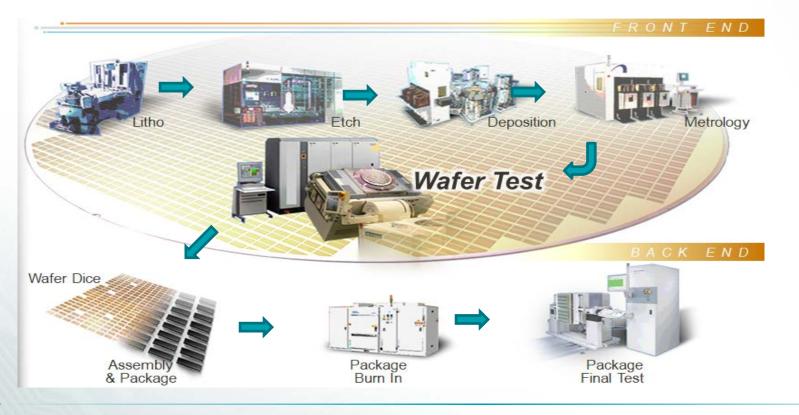

### Introduction: Where does Probe Card Needed in IC FAB Flow

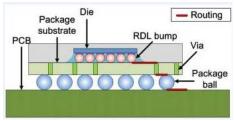

# Introduction: IC Packaging Technology – What're We Probing on

Wire-Bound

AI/Cu PAD

Large Pitch Microprocesso

#### **BGA Flip Chip Package**

#### **BGA Solder Bump**

Fine Pitch CPU & Mobile Processor

#### **CuPillar Flip Chip Package**

#### CuPillar w/wo Solder Cap

### Market Overview Flip Chip Packaging Trend – CuPillar will Take Major Market Share

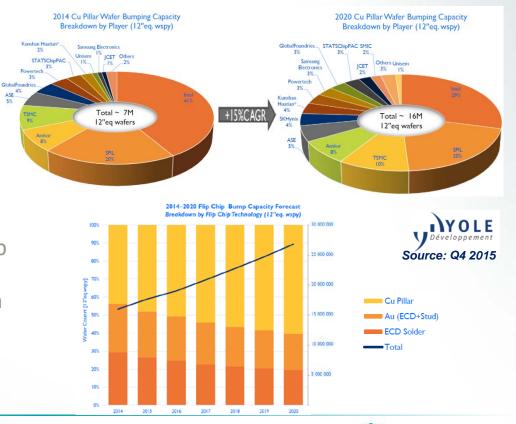

- Wafer capacity forecast increase from 16M (2014) to 26M (2020)

- CuPillar wafer bumping capacity increase from 7M (2014) to 16M (2020)

- CuPillar market expect to grow at CAGR(2014-20) of 15%

- > 50% of bumped wafers for flip-chip are now CuPillar packages

- Top 5 remain strong market position

### Market Overview Why moving into CuPillar packaging

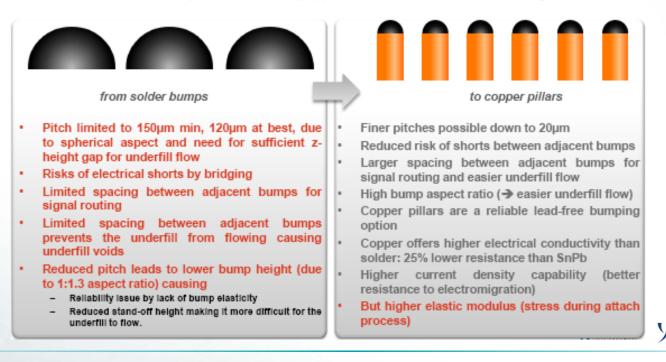

"Pillars" of copper are typically plated on the chip in wafer form through photolithography techniques. Solder bumps have fixed aspect ratios lower than one, whereas copper pillars offer aspect ratio flexibility, and therefore can increase I/O bump densities for many applications in addition to other advantages...

# Market Overview HVM CuPillar Probing Challenges

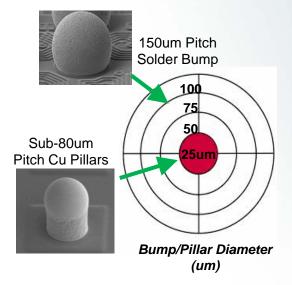

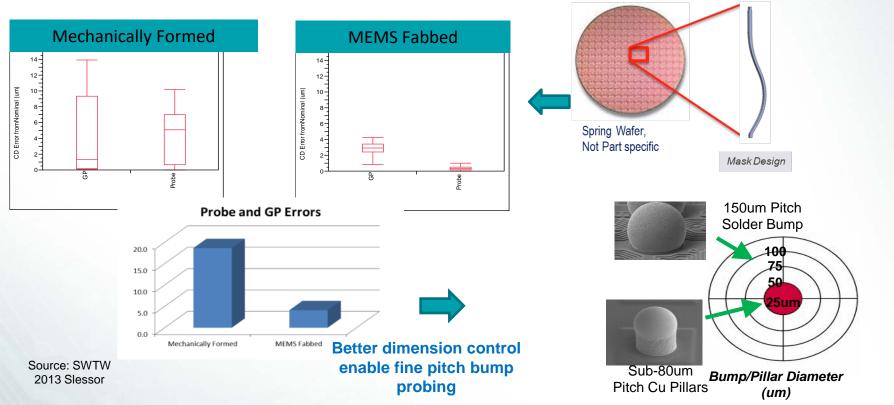

### Probing on 3x smaller solder bump

- Require micron-meter level probe tip alignment control

- Low vertical and lateral probe force for gentle touch down on small bump

### Maintain High Probe Card Up-Time on HVM

- Increase current protection limit while probe is thinner

### Probe Card Last through out the Product Life

- Longer life-time probe required while probe tip size is reducing

# FFI Cu Pillar Probing Solution Evolution

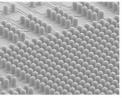

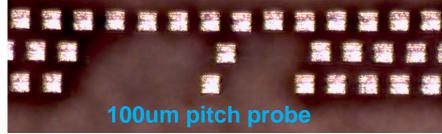

Started with 3mil, followed by 2.5mil, then MEMS for 100um Pitch and Below

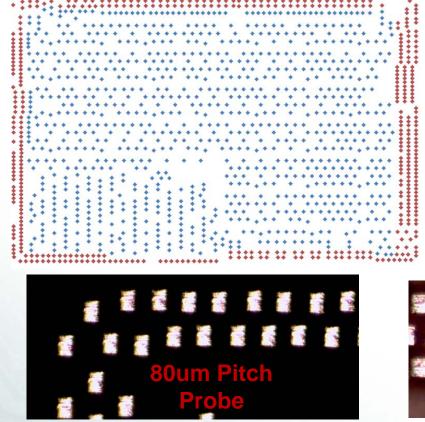

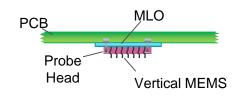

# MEMS Fabricated Vertical Probe Card for CuPillar Probing

#### Features Required for Fine Pitch CuPillar Probing

- Fine Pitch, 40um for TSV or Si Interposer Probing, 60/80um CuPillar Production Probing

- Low CRES, "No float" architecture for contact stability and thermal agility over wide temperature range

- High current capability, 1.5 A/probe CCC

- Long Life Time, Wear-resistive tip materials and geometries, ~ 2X longer lifetime vs. vertical at comparable bump pitch

- HVM Capability, Machine-assembled probe head for high throughput and superior quality, >30k pins per

card

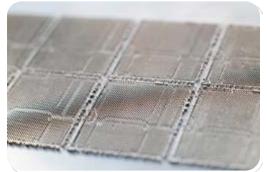

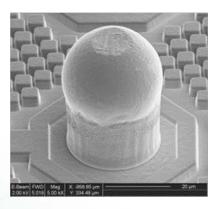

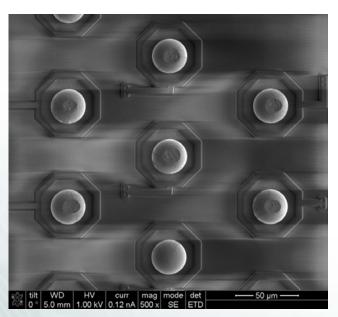

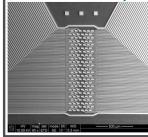

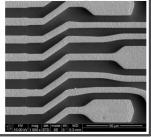

Composite MF80 MEMS Probe with different materials, at different locations, with micron-level precision

80um Pitch Grid-array MEMS Probe Head 30k pins, X8

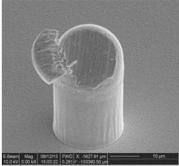

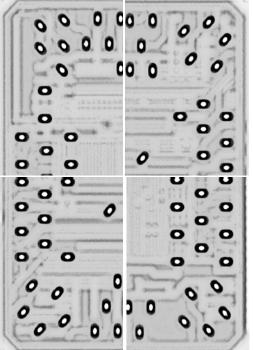

### CuPillar Probe Mark Photo Gallery Aiming accuracy and probe force are essentials to get good probe mark

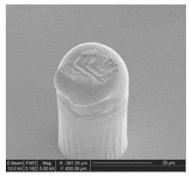

Pass Good Probe Mark on 30µm Cu Pillar

<u>No Pass</u> Cu Pillars with Sheared Solder Cap

<u>No Pass</u> Misaligned Probe Tip

<u>No Pass</u> Probe force too high

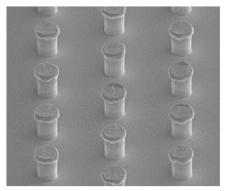

#### Dimensional Control Improved With MEMS Fabrication Processes Wafer Lithography and Plating

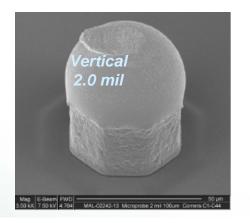

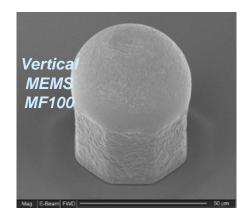

### Low Vertical & Lateral Probe Force is Essential Minimize CuPillar Impact, Better on Packaging Reliability

- Benefit of low-impact probing by MEMS Vertical Probe

- Minimizes solder material displacement on the solder surface

- Eliminate the need for additional reflow post wafer probing (due to solder damage)

- More even force at pillar footing for better packaging reliability

Probe Mark Comparison of Vertical MEMS MF100 vs. Vertical 2.0mil

### MEMS Vertical Probe Mark on 80um Pitch CuPillar Hot Temperature at 90°C

25um Cu Pillars Probe Mark at 75um OT

Cu Pillar Size: 96umx59um Probe Mark Size: 16um x 26um 80um OD

#### At max 125um OD Probe Mark still within 25%

| OD(0D1+?) | TD=? | P/M size X(um) | P/M size Y(um) | P/M(%) | P/M < 25% |

|-----------|------|----------------|----------------|--------|-----------|

| OD1+70    | TD=4 | 18             | 21             | 11.40% | Y         |

| OD1+80    | TD=4 | 16             | 24             | 11.60% | Y         |

| OD1+90    | TD=4 | 17             | 23             | 11.80% | Y         |

| OD1+100   | TD=4 | 17             | 26             | 13.30% | Y         |

| OD1+110   | TD=4 | 16             | 27             | 13.00% | Y         |

| OD1+120   | TD=4 | 17             | 27             | 13.80% | Y         |

| OD1+125   | TD=4 | 18             | 28             | 15.20% | Y         |

| OD1+70    | TD=6 | 17             | 25             | 12.80% | Y         |

| OD1+80    | TD=6 | 16             | 26             | 12.50% | Y         |

| OD1+90    | TD=6 | 17             | 27             | 13.80% | Y         |

| OD1+100   | TD=6 | 18             | 27             | 14.70% | Y         |

| OD1+110   | TD=6 | 17             | 28             | 14.40% | Y         |

| OD1+120   | TD=6 | 18             | 28             | 15.20% | Y         |

| OD1+125   | TD=6 | 18             | 29             | 15.70% | Y         |

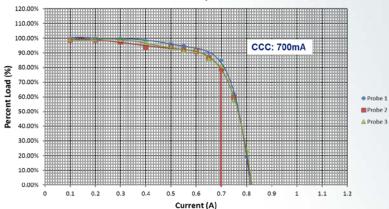

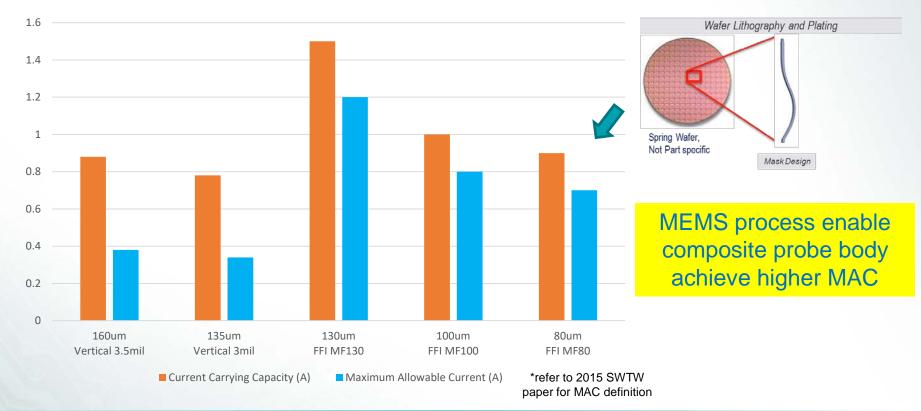

# **Current Carry Capacity Case Study**

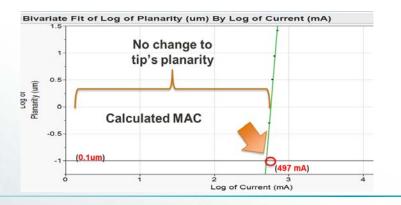

### Current Carrying Capacity (CCC)

- ISMI CCC: 700mA (at Room Temperature)

- Simulated CCC: 600mA (at 150°C)

- ISMI CCC is the current where the spring force is reduced by 20%, current duty cycle 2min on and 2min off

- Maximum Allowable Current (MAC)

- MAC 500mA (at Room Temperature)

- Calculated current associated with a 0.1um change in planarity, current duty cycle 1min on and 1sec off

60um Pointed tip Probe CCC

# **MEMS Probe Provides 2x Current Protection**

### Higher MAC, Less Burnt Probe Event Occur PC Always Stay at Production Line

### **Optimize the Probe Selection for Best Performance**

#### Hybrid MEMS Probe Design to Maximize Electrical & Mechanical Wafer Test Performance

SFORMFACTOR"

Amer Cassier, Engineer, Principal (Qualcomm Technologies, Inc.) Jarek Kister, Amy Leong, Ashish Bhardwaj (FormFactor Inc.)

June 4-7, 2017

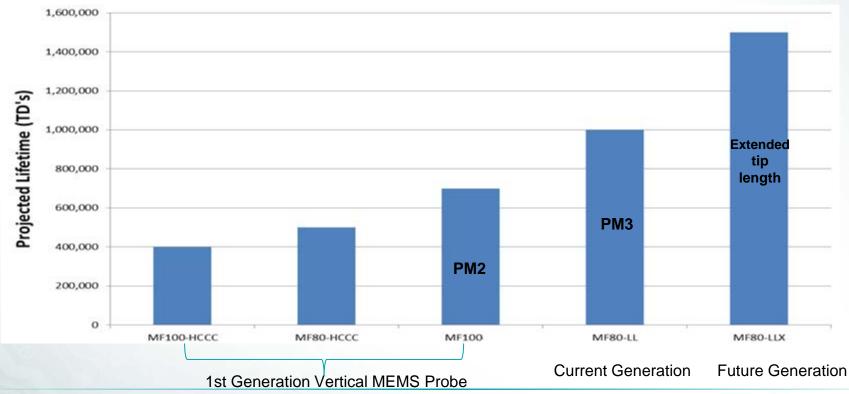

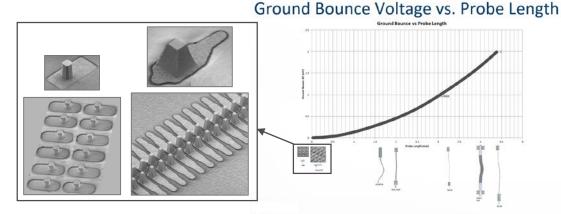

# **Vertical MEMS Probe Life-time Projection**

#### Vertical MEMS Probe Lifetime is a function of

- Tip Length How long is the usable tip length?

- The longer, the better. However...

- The longer, the worse aiming accuracy -> higher chance for misalignment or bump damage

- Need to consider optimal tip length for targeted application for production stability

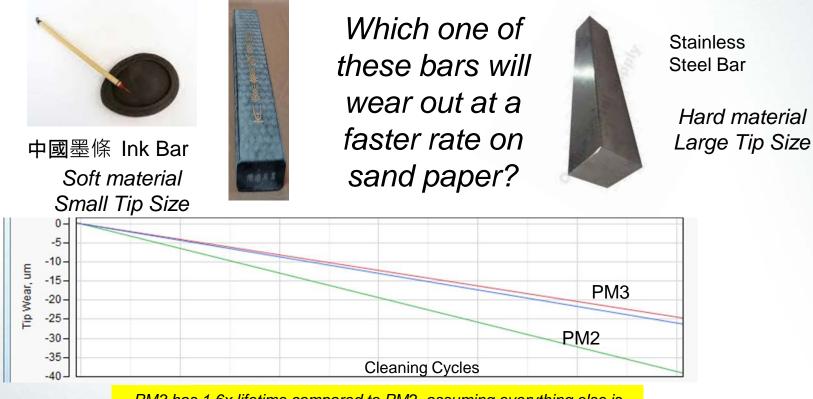

- Wear Rate How fast will the tip wear?

- Dependent on tip material, probe design, cleaning media/routines

- Traditionally no strong dependency for Cobra-style 3mil or 4mil, similar material/design

- "Smart" MEMS probe design can significantly slow down the tip wear rate

- **Cleaning Frequency** How often does the probe tip need to be cleaned to maintain yield stability?

- How sensitive is the device yield to Cres? How the tip material interact with probed pads/bumps?

- Need to be validated on custom wafers to ensure production yield stability

- "Pure Clean" Lifetime Projection

- This is the lifetime if only cycling on cleaning media without solder accumulation

- PureClean Lifetime = ( ( [Tip length] / [wear per 1k cTD]\*1000 ) / [#insertions] ) \* [CleaningInterval]

# Tip Size/Material Impact Life-time

PM3 has 1.6x lifetime compared to PM2, assuming everything else is the same (product architecture, tip size, probe force, etc)

# Continuously Extend Probe Life-Time with new probe alloy and optimize probe tip dimension

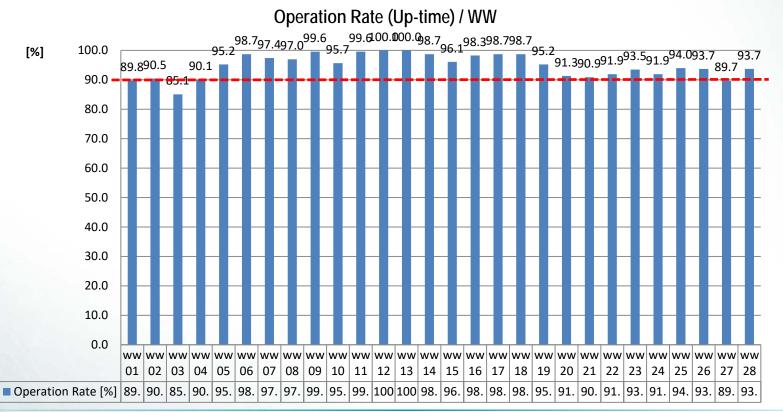

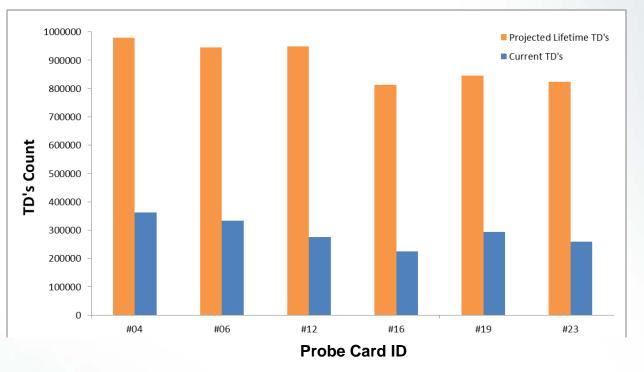

# MEMS Vertical Probe Life-time Study Projected Life-time Close to 1M Touch Down

- High-end mobile application processor x8 design, total ~30K probes

- MF80-LL on probing 80um Pitch CuPillar with solder cap

- Total 26 cards shipped

- Data collected by customer with 6 different cards

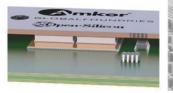

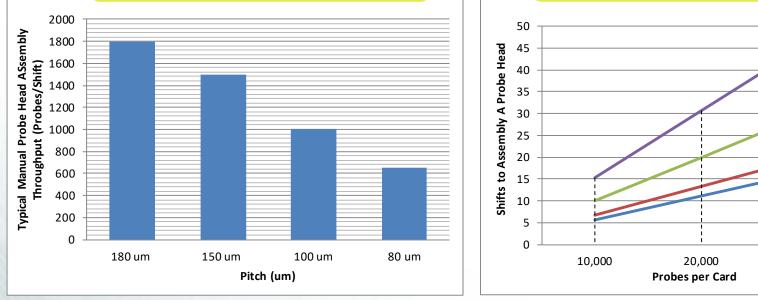

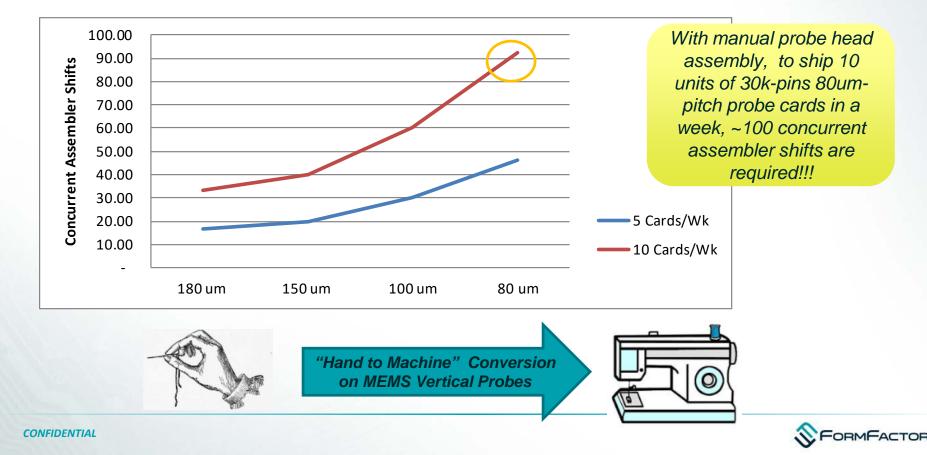

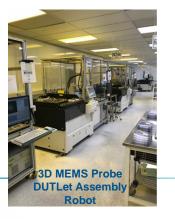

### Probe Assembly Throughput Is Becoming An Issue for Probe Card Cycle-time @ 80um CuPillar Pitch

Vertical Probe Assembly Throughput Decreases with Slimmer Probes Probe Head Assembly Is Becoming the Critical Path to Probe Card Cycle-time As Pin Counts/Probe Card Approaches 20k Pins

30,000

180 um

150 um

100 um

80 um

#### Time-to-Volume Ramp-up @ 80um CuPillar Pitch What if 10 cards are needed in a week to address peak demand?

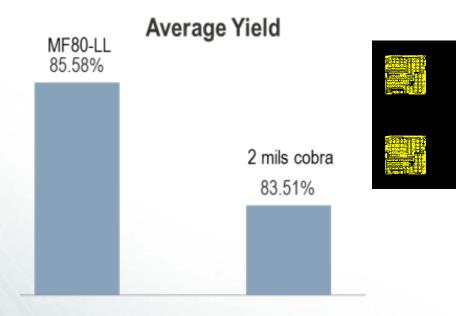

# MEMS vs. Conventional 2mil CuPillar Wafer Probing Yield Comparison

### Project Background

- MEMS 80um pitch and Conventional 2mils probe were used to compare yield on a mobile SoC design

- 85um pitch, 4-DUTs, 9k pins, 45x100um Oval-shape CuPillars

### Results

- MEMS Probe Head showed ~2.07% yield higher than conventional probe head

- Measured on customer site 3 Lot total 75 wafers.

# MEMS Technology Adoption in Advanced PC Market

- Total Advanced Probe Card Market continue growing to 2021

- CAGR (2016~21) 6.4%

- MEMS Probe Card contribute most market growth

- VLSI forecast MEMS PC market maintain CAGR (2016~21) 10.2%

- MEMS PC revenue surpass conventional vertical PC revenue since 2016

Foundry and Logic Advanced PC Market \$1.000 Source: VLSI Research \$900 \$800 \$700 \$600 \$342 \$308 \$500 \$213 \$178 \$400 \$145 \$11 \$300 \$200 \$100 \$-2012 2013 2014 2015 2016 2017 Conventional Vertical Probe Cards Other Advanced Probe Cards (RF) MEMS Probe Cards

### MEMS Technology for Fine Pitch CuP & Advanced Packaging Testing

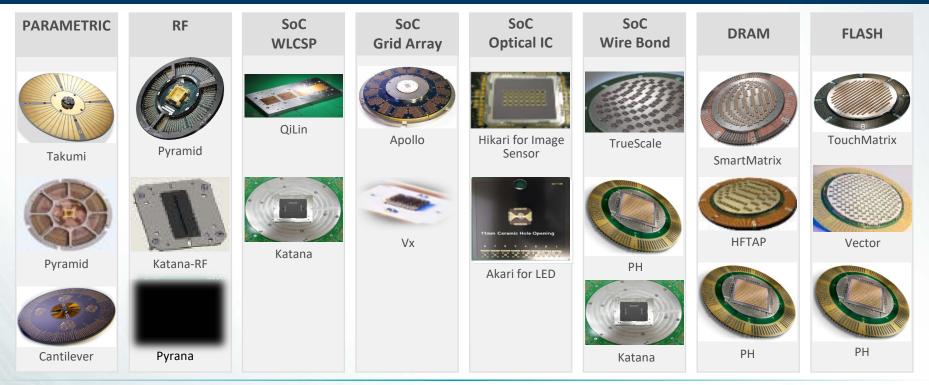

# FormFactor Probe Card Product Portfolio

#### Addressing a Wide Range of Test Cost and Application Requirements

### FormFactor/Cascade Combined Technologies Enabling Next-generation IC Test Challenges

- World largest MEMS fab for probe card application

- 2D MEMS, 40 & 30um pitch solution for wafer & 2D+ PKG/TSV test

- 3D MEMS, new material capable >175C for **automotive & high temp** test

- RF MEMS, low inductance and 50Ωn impedance probe for **HF 5G application**

- Fine pitch Space Transformer, MLO or MLC, Metalized Guide Plate

#### ROBOTIC CAPABILITY

- Fully-automated 2D probe assembly capability

- DUTlet assembly at micron-level precision in x/y/z

#### DESIGN AUTOMATION

- Touchdown optimization (TDO) and Total Cost of Test (TCoO) Analysis

- Advanced Tester Resource Extension (ATRE), ie. Power resource splitter

- Tester channel to DUT channel assignment optimization

#### ENGINEERING SYSTEM CAPABILITY

- CM300xi for singulated die testing on carrier

- Estrada-EM for TSV electro-migration defect detection and measurements

Custom IC

MEMS ST : 5um Space & Trace, 55um pitch

Fully-Automated 2D MEMS Probe Assembly Robot

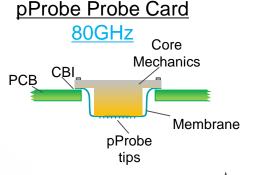

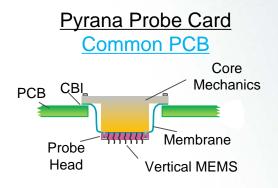

# Production Probe Card for Radio Frequency Testing

#### Cover from 5GHz to 80GHz

- RF Performance: >80GHz

- Space Transformer: Membrane

- Max Area: 10 x 38mm

- Common PCB: Possible

- Pin Repair: No

- Pin-Pin Compliance: +/-20um

- NPI Leadtime: 5-8 weeks 🔀

- Status: Released to Production

Katana-RF Probe Card High Parallelism

- RF Performance: <10 GHz

- Space Transformer: MLO

- Max Area: ~75 x 75mm

- Common PCB: No

- Pin Repair: Yes 🔀

- Pin-Pin Compliance: +/-100um 💢

- NPI Leadtime: 8-12 weeks

- Status: Released to Production

- RF Performance: <10 GHz

- Space Transformer: Membrane

- Max Area: 10 x 75mm

- Common PCB: Yes 🔶

- Pin Repair: Yes 🔀

- Pin-Pin Compliance: +/-100um 🔀

- NPI Leadtime: 6-9 weeks <del>\/</del>

- Status: In Pilot

\*CBI: interface from membrane to PCB, common PCB to support multiple probe heads

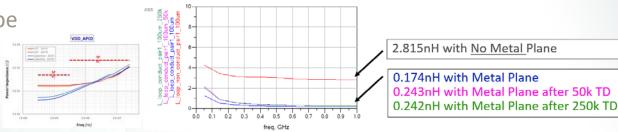

# R&D Focus – High Frequency/PDN in Wafer Test

- Enable Wafer Test results Equivalent to Package Test Performance

- Approach: Low inductance probes, Innovating probe shielding

- Short probe length, 200um

- Metalized GPs

- 50 Ohm Impedance probe

#### MF80-48 Loop Inductance Improvement 100micron pitch metalized Initial vs. 50k TD & 250k TD 1-port Measurement with Network Analyzer

# FormFactor's Leadership in Advanced Probe Cards

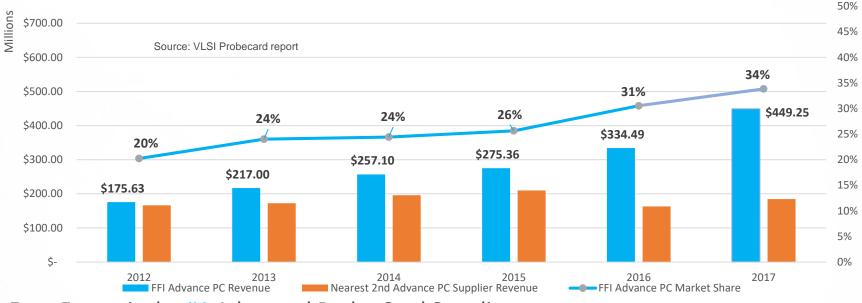

Formfactor Advanced PC Revenue and Market Share

FormFactor is the #1 Advanced Probe Card Supplier

- Consistently growing market share leadership 6 years in the row

- Continued R&D and Support investments to innovate and enable smooth production

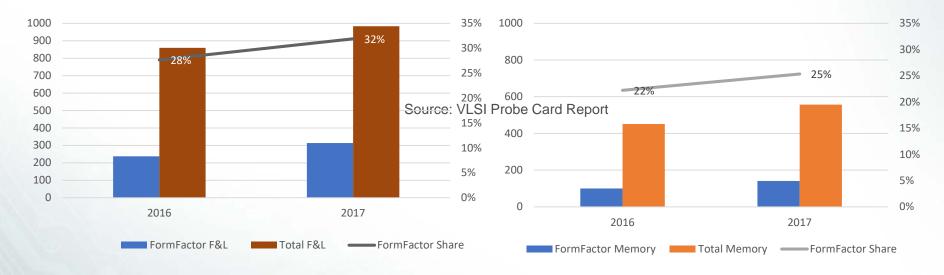

# FormFactor #1 Logic and Foundry Probe Card Supplier

# Logic and Foundry Probe Card Market:

- 2017 total logic and foundry PC market ~\$984M

- Formfactor #1 market share at 32%, fastest growing in 2017 by ~\$76M

### **FormFactor China**

- Founded in 2006, about 80 employees

- \$1.5M investment to expand capacity & service capability in China

- Suzhou open house in September 2016– "10 Years and Counting"

# Advanced Tooling Capability

URS,PRVX3, PRVX4(the 1<sup>st</sup> advanced probe card test system in China), DD sanding station and metrology tool in place

Figure 1. PC URS (Probe Card Universal Repair Station)

# Conclusion

- Static trend of SoC flip chip packaging technology is moving into CuPillar

- In 2016 >50% of wafer bumping with CuPillar package

- CuPillar market expect to grow at CAGR of 15% through out 2020

- Conventional probe technology reaches its limitation on testing fine pitch CuPillar

- Alignment accuracy, probe force, current carrying capability

- MEMS probe technology is required for fine pitch CuPillar HVM testing

- Micro-meter level probe tip aiming accuracy

- Low 3D probe force

- Higher maximum allowable current

- Lower probe tip ware-out rate

- High throughput and superior quality