# TEST VISION Symposium

### **TEST'S ROLE IN UNITING THE INDUSTRY**

### **Probecard Challenges for Expanding Arrays of Fine Pad Pitch Devices to Test Under Wide Temperature Range**

### Pouya Dastmalchi, Ph.D.

Application Eng. Manager

## Agenda

- Motivation of Work

- Continued strong growth in the wire bond, automotive IC market

- Expanding challenges and trends for wire bond probing

- Development Strategy Overview

- Architectural Strategy

- Product Overview

- Product Validation Results

- Internal Validation Results

- External Validation Data

- Summary and Acknowledgements

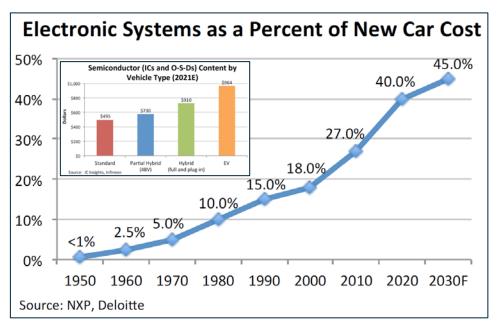

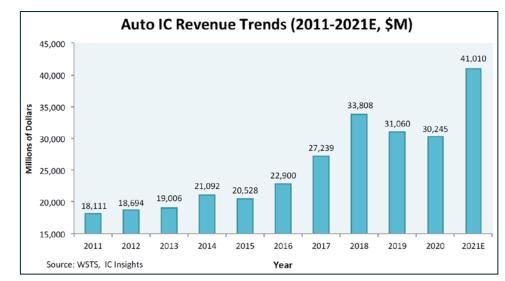

### **Automotive Semiconductor Market Overview**

- Automotive electronics is a fast-growing market

- Semiconductor-built electronics is expected to approach nearly half the cost of a new car early next decade.

- In 2021 Automotive IC Market size increased to ~\$41B

- Expanding at a CAGR of 6.2% from 2021 to 2028.

- Requirements for automotive applications:

"Unlike semiconductors intended for use in consumer electronics, automotive semiconductors must retain functionality in more extreme environments (colder and hotter temperatures) for longer periods of time", The Automotive Semiconductor Market, USITC, May 2019

### The Impact of Automotive Requirements for Semi Wafer Test

#### • Critical requirements for automotive semiconductor test

- Test temperature extremes continue to increase

- Increased complexity of peripheral pads layout

- Pad pitch continues to shrink

- Pad sizes are being reduced to support die size shrinks

- Dense device circuitry under the pads

- Devices can be sensitive to CRES and CRES variation

- IC suppliers driving reduced costs

- Drives need for **increased parallelism →** LAA

Typical Wire Bond Device

#### Increased Temp. extreme

#### Dense under pad circuitry

|                               | Crack3 | Crack2    | Crack1              |

|-------------------------------|--------|-----------|---------------------|

| Pt coating<br>IMID<br>Metal 2 |        | E         |                     |

| IMD<br>Metal 1<br>ILD         |        |           | Augs sugs in 2020.1 |

|                               | -      | Condicits |                     |

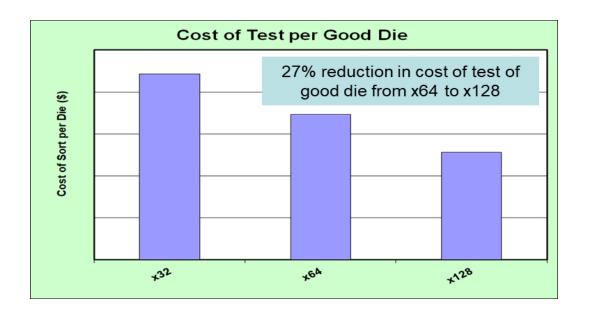

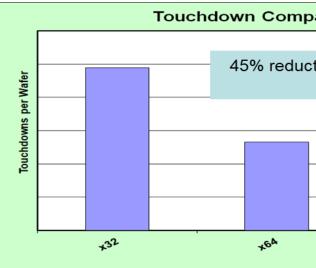

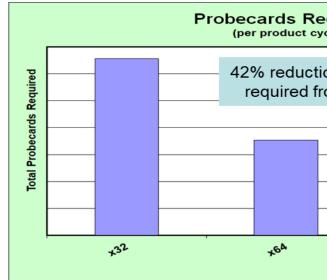

## **Meeting Cost of Test Reduction Challenges**

#### Reduce cost of test with increased parallelism

- TCOO analysis

- Key Assumptions:

- o 5.0mm x 5.0mm die size

- o 300mm wafer

- o 30 sec test time

| arison                          |

|---------------------------------|

|                                 |

| tion in TDs from x64<br>to x128 |

|                                 |

|                                 |

|                                 |

|                                 |

| ***28                           |

|                                 |

| equired                    |      |  |

|----------------------------|------|--|

| on in probe<br>om x64 to x |      |  |

|                            |      |  |

|                            |      |  |

|                            |      |  |

|                            | *128 |  |

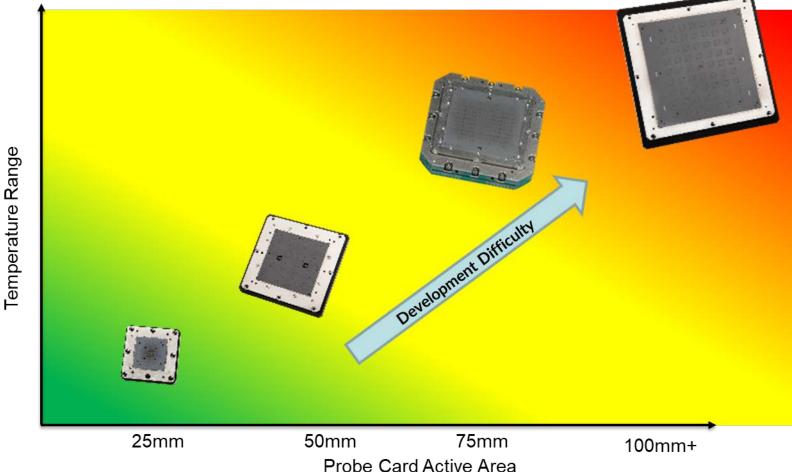

### **Increasing Probe Card Active Area**

- Increasing parallelism requires increased probe head active area

- Presents significant development challenges to overcome to meet probing requirements

- Must consider critical requirements

- Thermal effects

- **Device Layouts**

- Pad size/pitch

- Electrical

As PH sizes and thermal requirements increase, CTE mis-match issues become significant challenge to overcome

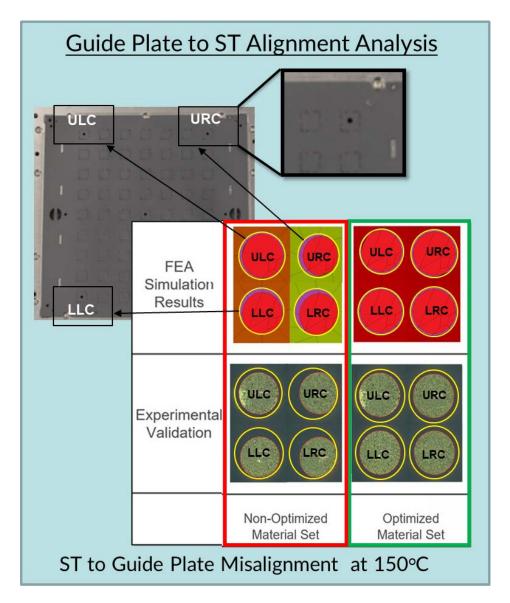

## Large Active Area Vertical PC Material Selection Strategy

- Three step process used to optimize the materials of various LAA probe card components:

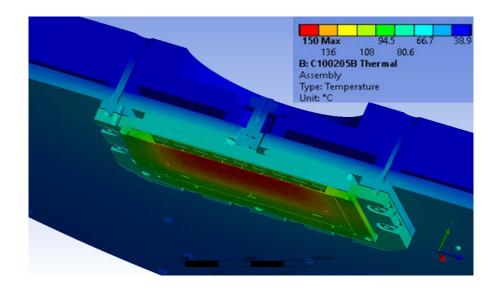

- 1. Prediction of thermal gradient on various components of the probe card by use of FEA simulation for the full temperature range

- Chuck temperature of 150°C, 100°C temperature delta between the coldest and hottest components

- **Optimal material selection:** 2.

- Use thermal gradient derived from step one as input to thermal-mechanical model

- Predict misalignment between various components and select best material combinations

- **Experimental validation** of optimal material 3. set for the full probe card build

- Thermal model of a probe card with prober chuck temperature set at 150°C

- Model includes:

- Ο

- 0 members

- **Radiation** between the wafer and probe card Ο

- $\cap$

#### **Thermal conduction** of all parts of the assembly **Contact conductance** between the different horizontal

Air conduction between the wafer and PCBA

## **Vertical PC Components Material Selection Challenges**

| Component              | Consideration                                              | Solution                     |

|------------------------|------------------------------------------------------------|------------------------------|

| Guide Plates           | CTE has direct impact on wafer<br>bond pad size capability | Best match to customer wafer |

| Space Transformer (ST) | ST to probe misalignment                                   | Best match to guide plate    |

| Mounting Hardware      | ST to probe misalignment                                   | Best match to ST             |

- Based on requirements of peripheral pad probing, FFI developed a solution based on a Multi-Layer Ceramic (MLC) ST

- Advantages include:

- Low to moderate levels of CTE of the MLC → stable thermal-mechanical performance

- 2. ST flatness  $\rightarrow$  good probe planarity

- Optimized material set → stable thermal-mechanical performance

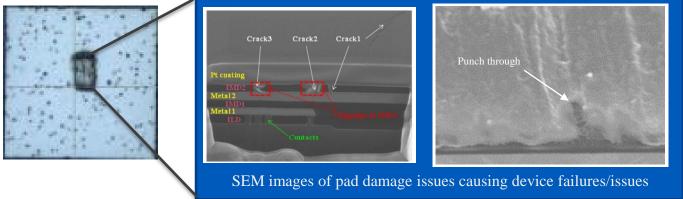

## **Bond Pad Integrity – Minimize Pad Damage**

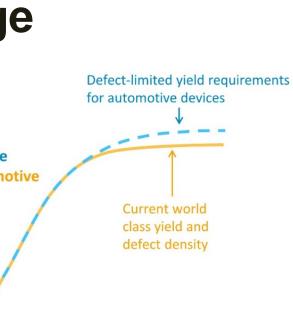

- "Reliability expectations for automotive devices are orders of magnitude higher than consumer devices"

- Bond pad damage must be held to a minimum both surface area and depth

- Need clean area for bonding the device

- Zero tolerance for ILD cracking for UPC damage

| Increasing Yield →<br>Decreasing D0 → | Automotive<br>Non-Autom |

|---------------------------------------|-------------------------|

|                                       | 0%                      |

|                                       | Automo                  |

|              | Low Force MEMS<br>Springs                                            | Medium/High Force<br>Springs                                                     |

|--------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Spring Force | 1.2 – 1.5 grams at<br>production OT to support<br>minimal pad damage | 4 - 12 grams at production<br>OT - High force can create<br>excessive pad damage |

otive IC Industry Trends – Semiconductor Engineering – Jan. 2018

Time

## Meeting the Challenges of LAA Vertical Probing

- Requirements:

- Thermally stable vertical spring architecture to support wide temperature range of automotive test requirement

- Tight pad pitch, multiple pad rows, core pads

- Probe on small pads with minimal pad damage

- Stable electrical performance low, stable CRES

- Increase parallelism to reduce cost of test

- **Kepler<sup>™</sup> Vertical Probe Card Features**:

- Utilizes Multi-Layer Ceramic (MLC) space transformer

- Proprietary fine pitch, low force vertical 2D MEMS springs

- Full planarity/tilt adjustment capability

- Flexible probe head configuration to support various device layouts, array sizes and pad pitch requirements

- Service friendly architecture field replaceable springs and components

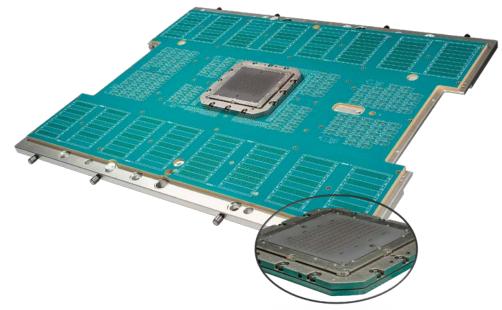

#### 128 site, 60um Pitch, 10K Probes, V93K DD

## **Experimental and Qualification Results**

### • Low force spring performance

- ✓ 60um pad pitch capable

- Scrub mark results

- ✓ Minimal pad damage and placement

### • Thermal performance

✓ Scrub mark position at temperature extremes

### • Planarity results

✓ Capability at 75mm active area

### CRES performance

✓ Stability at temperature

### Lifetime study

✓ Confirm low wear rate

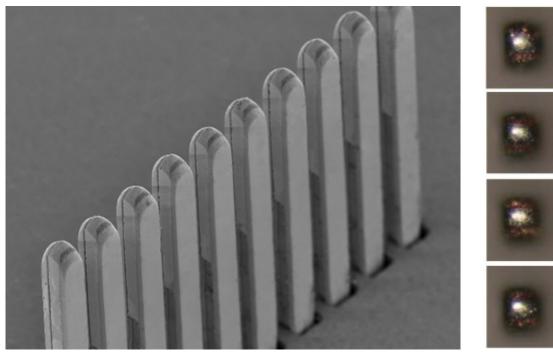

## FFI MF Family Low Force 2D MEMS Spring

• Utilizing FFI low force 2D MEMS MF spring family, developed a solution for 60um pitch pads applications

60um pitch SEM and Optical Images

60um pitch probe marks on 55x65um Al pads @ 125C (100um OT)

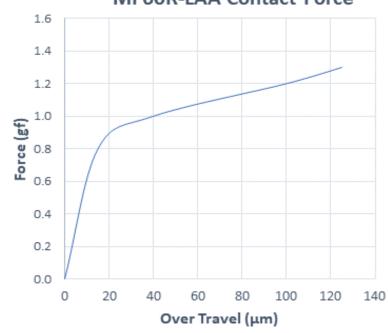

#### MF60R-LAA Contact Force

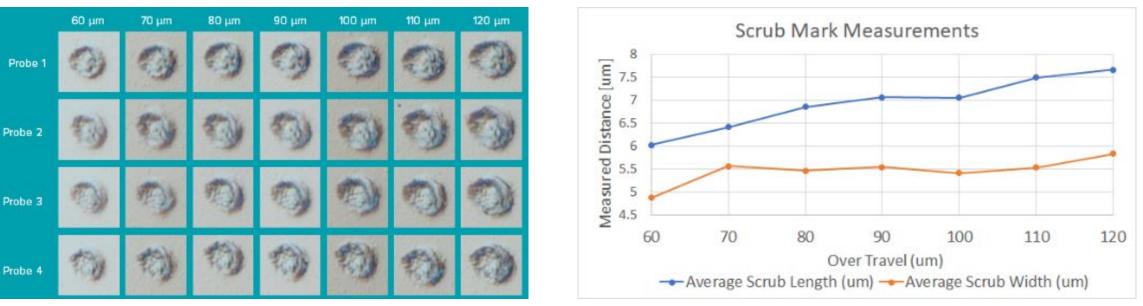

### **Scrub Mark Results**

Optical images of scrub marks

- MF60R minimizes pad damage

- Small scrub mark from low force vertical spring minimizes pad damage area

- Very low risk of punch through due to small scrub mark with minimal lateral scrub

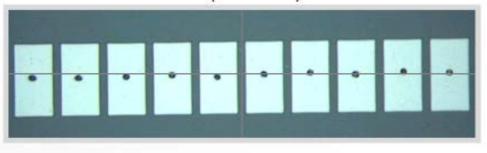

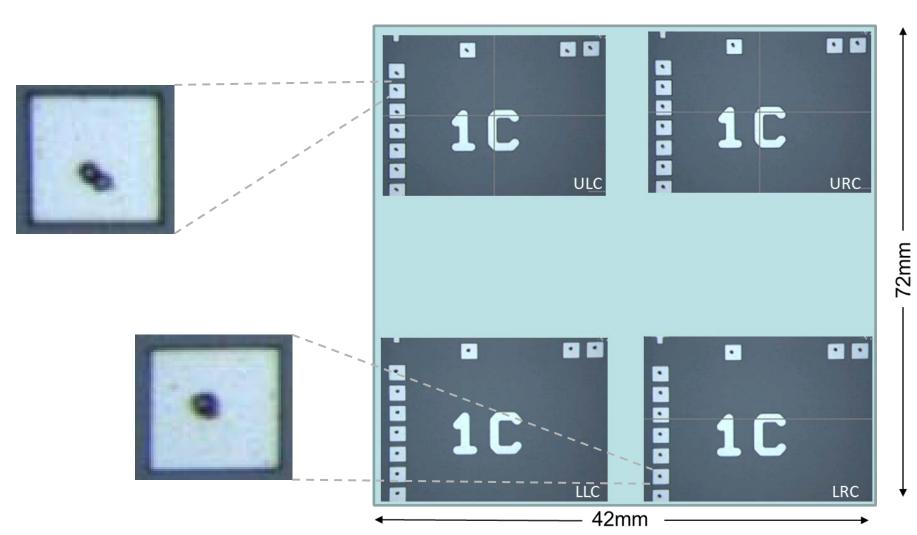

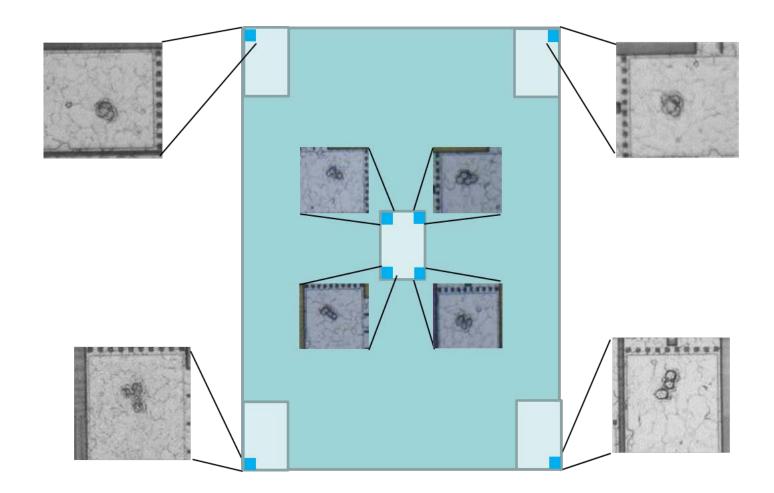

### **Kepler**<sup>Thermal-Mechanical Performance</sup>

#### • Experimental set-up:

- Parallelism: x128

- Array size: 42mm x 72mm

- Pad size: 55um x 55um

- TD data collected at -40°C, 25°C and 150°C

- Scrub mark images from upper right corner of die from four corners of the array

Scrub marks from temp range of 190°C landing in same pad area across the full PH array

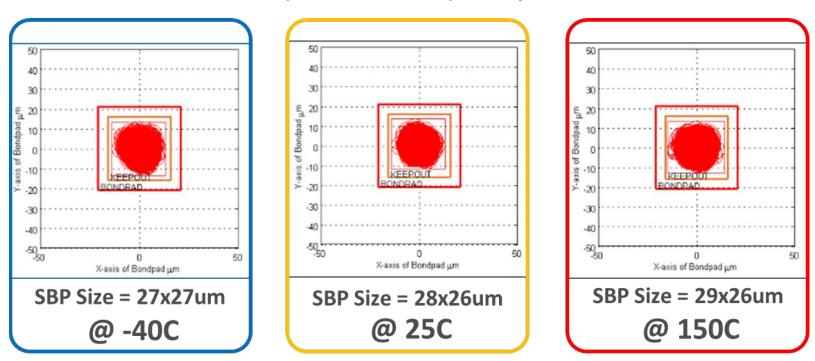

## Super Bond Pad Capability at Full Temp Range

### • Super Bond Pad (SBP):

- Consolidation of scrub marks superimposed on top of each other to establish a single virtual pad representing all scrub marks

- SBP calculation removes systematic errors not associated with the probe card capability

- Parallelism: x128

- Array size: 42mm x 72mm

- Pad size: 42um x 42um

- Keep out: 5um

- 100% of scrubs in pad area meeting the keep out spec

SBP performance <30um per side through entire temperature range

IN CONJUNCTION WITH

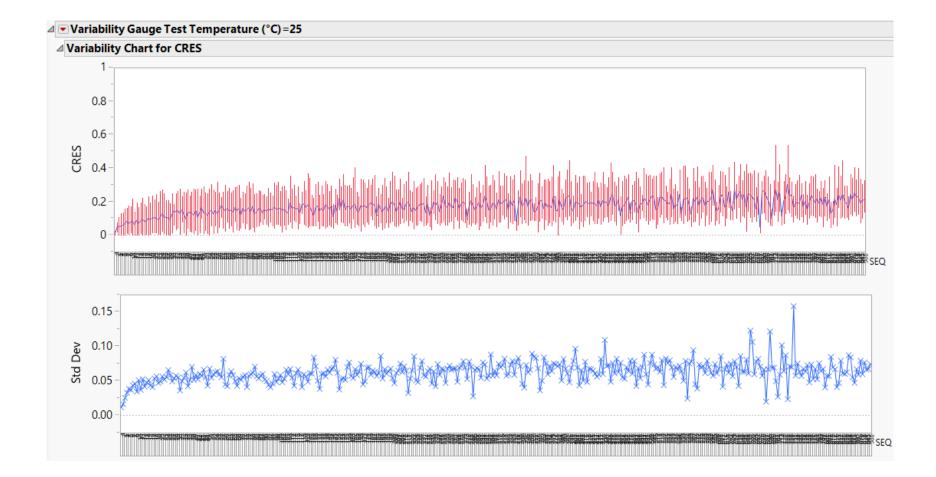

## **CRES Performance at Room Temperature**

### • Test Conditions:

- Blank Al wafer

- Over Travel: 100um

- Number of TDs: 1000

Kepler<sup>™</sup> achieves low and stable CRes

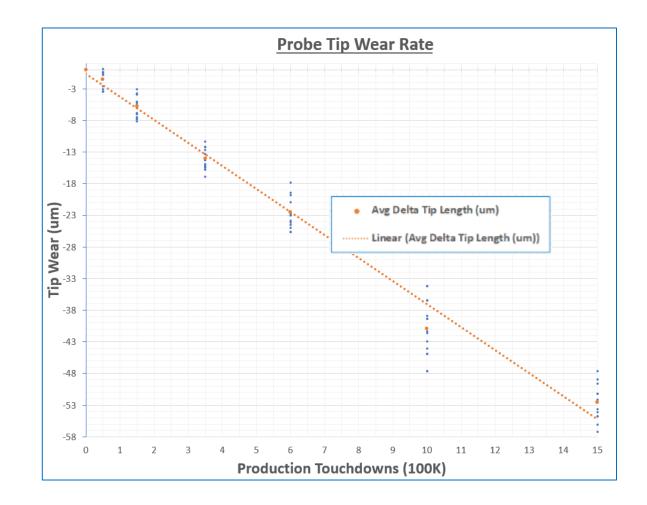

### **Wear Rate Study Results**

- Objective:

- Establish probe tip wear rate during production use case

### • Experiment:

- Accelerated study 100um OT on Al pads

- Tip length was measured at 50K, 150K, 350K, 600K, 1M, and 1.5M TDs

- Optimized cleaning recipe with WA6000-SWE

### Data projects >1.5M Touch-Down lifetime

### Large Active Area Planarity Performance

- Planarity measured on large active area array:

- Array size: 42mm x 72mm

- Parallelism: x128 \_

- Measured outgoing planarity on PRVX showed <20um on entire array

| Planarity | Min.    | Max.    |

|-----------|---------|---------|

| 19.9 um   | -7.9 um | 12.0 um |

Incoming planarity collected with contact check for first to last electrical touch confirmed ~25um planarity across full array

OD=20

OD=30

OD=40

OD=50

## **Thermal-Mechanical Performance – Customer Validation**

#### • Experimental set-up:

- Parallelism: x128

- Array size: 42mm x 72mm

- Pad size: 42um x 42um \_

- TD data collected at 150°C ,-40°C, 25°C and repeated at 150°C

- Scrub marks at all edges of the array landing in very small area – minimal pad impact

Architecture demonstrating very stable scrub mark placement from -40°C to 150°C

IN CONJUNCTION WITH

## **Summary**

- Strong automotive IC market growth requiring large active area solutions for wire bond applications

- FFI has developed a large active area vertical probe card solution

- Addressed challenges related to CTE mis-match to meet increasing test requirements \_

- Thermal-mechanical stability over wide temperature \_

- Tight pad pitch —

- Small pad sizes —

- Tight planarity and scrub mark position \_

- Stable and low CRES

- Long life-time \_

- Flexible low force vertical MEMS architecture to reduce cost of test with increasing multi-site capability \_

## Acknowledgements

### **Special thanks to:**

- Mark Ojeda Infineon Technologies

- Cameron Harker FormFactor

- Yohannes Desta FormFactor

- John Muir FormFactor

- Doug Ondricek FormFactor