FormFactor has now made available Dr. Hadi Najar’s COMPASS presentation – Maximizing CCC in a Probe Card and the March to an Unburnable Probe. The Senior Principal Engineer discusses why CCC matters, reviews a hybrid probe configuration, introduces the next generation probe that FormFactor is introducing, reviews the metallized guide plate, and looks at different configurations and how they maximized the CCC.

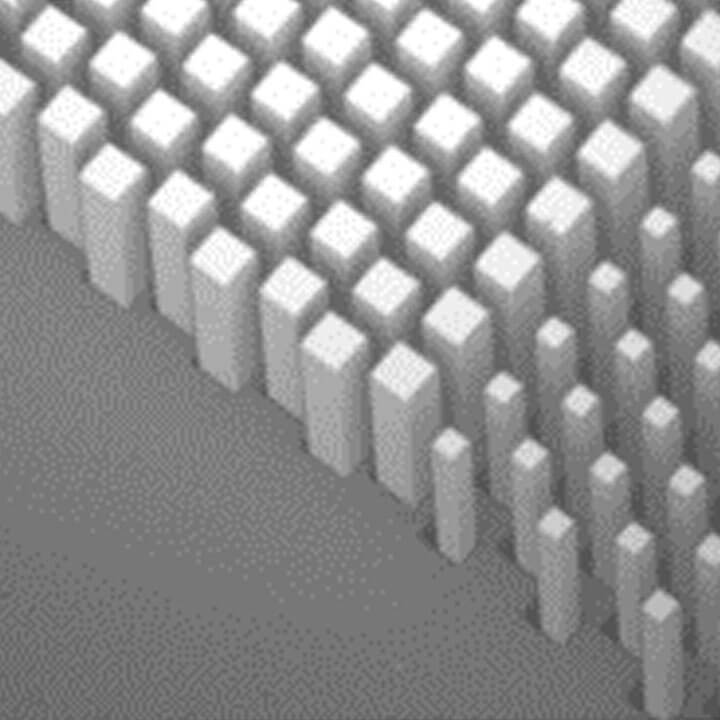

Datacenters and High-Performance Compute (HPC) applications are rapidly approaching, and in some cases surpassing, 1kW of total power for a single chip under normal operating conditions. The shift to new semiconductor nodes exacerbates this trend by increasing power density, which presents significant challenges for power and thermal management during device testing—even in low-power applications like mobile application processors. This escalation in device power output poses several challenges for wafer testing, especially in maintaining contactor integrity under high current and high-temperature conditions. To manage this, it is crucial to enhance the current carrying capacity (CCC) of probes during testing to keep pace with the rising power levels observed in the device under test (DUT). This results in improved uptime and reduced testing costs. This presentation discusses various strategies that can be implemented in probe card design to maximize CCC, aiming to achieve an effective CCC of greater than 2.5A at an 80um minimum pitch. These strategies include both new probe developments and architectural enhancements to sustain probe integrity in high-stress, high-current environments.

The key to maximizing effective CCC lies in optimizing the ratio between probe body resistance and contact resistance to the middle guide plate. Plotting this relationship reveals that increasing the number of probes in the net asymptotically approaches maximum ECCC.

Validation of the model through experimental data confirms its accuracy, showing an average improvement of 65% for 20 connected probes. Further analysis considers real cases, discussing the effect of current spikes and how connecting probes mitigates their impact.

Design challenges include the complexity of connecting numerous probes in a probe card. Automation of this process minimizes errors and reduces cycle time from weeks to hours, facilitating efficient probe card design.

To watch the video presentation, click here.